# PHY1090

### 10GbE Linear Transimpedance Amplifier

### **Features**

- 1100nA<sub>rms</sub> maximum input referred noise

- Linear up to 2mA<sub>pp</sub> input level

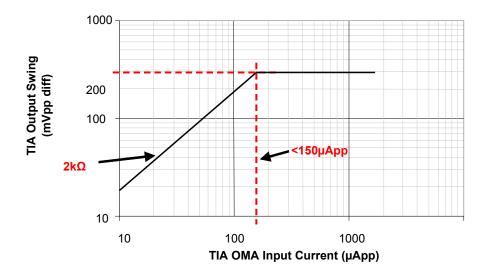

- 2kΩ typical transimpedance

- Incorporates automatic gain control

- 3.3V power supply

- Integrated PIN filter capacitor & resistor

- OMA-based RSSI output current

- -40°C to +95°C operating range

- 1.169mm X 0.929mm die size

## **Applications**

- EDC enabled receivers

- OC192 Telecom systems

- IEEE 10GBASE-LRM receiver systems

### Description

The PHY1090 is a high linearity transimpedance amplifier designed to be used in fiber optic modules for EDC enabled 10Gbps applications. The PHY1090 is optimised for applications requiring low distortion and low input referred noise, such as 10GBASE-LRM. When combined with the PHY2060 EDC IC, the PHY1090 enables a complete EDC-enabled receive path, ideally suited to the 10GBASE-LRM IEEE standard.

The PHY1090 integrates a low noise transimpedance amplifier and an automatic gain control output stage to give a linear output over a wide dynamic range. It also integrates an RC filter in series with the photodiode cathode pads to reduce ROSA cost.

Figure 1: Block diagram

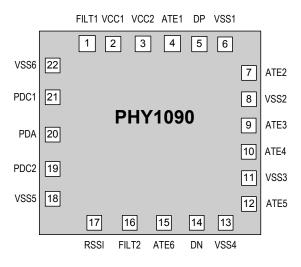

Figure 2: Pad Layout

PHY1090-RD-1.3

# 1. Ordering Information

| Part Number  | Description                     |

|--------------|---------------------------------|

| PHY1090DS-WR | PHY1090 bare die in waffle pack |

| PHY1090DS-FR | PHY1090 bare die on film        |

# 2. Pad Descriptions

| Number | Name  | Туре      | Description                                           |  |

|--------|-------|-----------|-------------------------------------------------------|--|

| 1      | FILT1 | Analog    | Series resistor to PDC, connected internally to FILT2 |  |

| 2      | VCC1  | PWR/GND   | Power supply connection                               |  |

| 3      | VCC2  | PWR/GND   | Power supply connection                               |  |

| 4      | ATE1  | Test pads | Probe test pad - Do not bond to these                 |  |

| 5      | DP    | Analog    | Serial data output+                                   |  |

| 6      | VSS1  | PWR/GND   | Ground connection                                     |  |

| 7      | ATE2  | Test pads | Probe test pad - Do not bond to these                 |  |

| 8      | VSS2  | PWR/GND   | Ground connection                                     |  |

| 9      | ATE3  | Test pads | Probe test pad - Do not bond to these                 |  |

| 10     | ATE4  | Test pads | Probe test pad - Do not bond to these                 |  |

| 11     | VSS3  | PWR/GND   | Ground connection                                     |  |

| 12     | ATE5  | Test pads | Probe test pad - Do not bond to these                 |  |

| 13     | VSS4  | PWR/GND   | Ground connection                                     |  |

| 14     | DN    | Analog    | Serial data output                                    |  |

| 15     | ATE6  | Test pads | Probe test pad - Do not bond to these                 |  |

| 16     | FILT2 | Analog    | Series resistor to PDC, connected internally to FILT1 |  |

| 17     | RSSI  | Analog    | Current proportional to OMA in dBm                    |  |

| 18     | VSS5  | PWR/GND   | Ground connection                                     |  |

| 19     | PDC1  | Analog    | Photodiode cathode connected internally to PDC2       |  |

| 20     | PDA   | Analog    | Photodiode anode                                      |  |

| 21     | PDC2  | Analog    | Photodiode cathode connected internally to PDC1       |  |

| 22     | VSS6  | PWR/GND   | Ground connection                                     |  |

### 3. Device Specifications

#### 3.1 Absolute Maximum Ratings

| Parameter              | Conditions      | Min  | Тур | Мах  | Unit |

|------------------------|-----------------|------|-----|------|------|

| Supply voltage         |                 | -0.5 |     | 6    | V    |

| Storage temperature    |                 | -55  |     | +150 | °C   |

| PDA Input Current A.C. | ER = ∞          |      |     | 4.0  | mApp |

| PDA Input Current D.C. |                 |      |     | 2.0  | mA   |

| Operating temperature  | Measured on die |      |     | 115  | °C   |

| Die attach temperature |                 |      |     | 400  | °C   |

Please note that functional device operation at these ratings is not guaranteed, nor implied. Sustained stress at these ratings may affect device reliability.

### 3.2 ESD and Latch Up Ratings

| Parameter Conditions      |                                | Min | Тур | Max | Unit |

|---------------------------|--------------------------------|-----|-----|-----|------|

| ESD – All pins except PDA | JEDEC JESD-A114 (HBM) Class 1c | 2   |     |     | kV   |

| ESD – PDA pin             | JEDEC JESD-A114 (HBM) Class 1c | 1   |     |     | kV   |

The device is not guaranteed to meet parametric specifications. Permanent damage may be incurred by operating beyond these limits.

### 3.3 Operating Conditions

| Parameter             | Conditions                   | Min  | Тур | Max  | Unit |

|-----------------------|------------------------------|------|-----|------|------|

| Supply voltage        |                              | 2.95 | 3.3 | 3.65 | V    |

| Operating temperature | Measured on back side of die | -40  |     | +95  | °C   |

#### 3.4 Parametric Performance

Parametric performance is guaranteed over the specified Operating Conditions.

### **DC Specifications**

| Parameter Conditions                              |                                               | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|-----------------------------------------------|------|------|------|------|

| Supply current                                    | Supply current Vcc = 3.3V                     |      | 45   | 68   | mA   |

| Power supply                                      | (VDP - VDN) / ΔVcc at 2MHz; no Vcc decoupling | 6    |      |      | dB   |

| rejection ratio                                   | (VDP - VDN) / ΔVcc at 5MHz; no Vcc decoupling | 14   |      |      | dB   |

| Input bias voltage                                | nput bias voltage PDA voltage; wrt Vss        |      |      | 1    | V    |

| Transimpedance At 10MHz;<br>Input current =40uApp |                                               | 1600 | 2000 | 2700 | Ω    |

| Photodiode filter resistor                        |                                               | 160  | 200  | 300  | Ω    |

| Output resistance Differential                    |                                               | 80   | 100  | 120  | Ω    |

### **AC Specifications**

| Parameter                              | Condition                                                                                          | Min | Тур | Мах  | Unit  |

|----------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| -3dB Bandwidth <sup>1</sup>            | Over input current range:<br>150uApp - 1mApp, 100Ω differential<br>output load                     | 5   | 6   |      | GHz   |

| Input current <sup>1</sup>             |                                                                                                    |     |     | 2    | mApp  |

| Input referred noise <sup>1</sup>      | Measured using 7.5GHz 4th order<br>Bessel filter;<br>Input current ≤ 150µApp                       |     |     | 1100 | nArms |

| Differential output swing <sup>1</sup> | Input current ≥ 150µApp, 10.3Gbps data<br>filtered by 2.25GHz, 4th order Bessel-<br>Thomson filter | 240 | 300 | 360  | mVpp  |

| Differential output swing <sup>1</sup> | Input current ≥ 150µApp<br>- 10.3Gbps back-to-back                                                 |     | 200 |      | mVpp  |

| Low frequency cut-off                  | 23uApp                                                                                             |     |     | 15   | kHz   |

| Output return loss, differential       | < 5GHz                                                                                             | 8   | 20  |      | dB    |

| Output return loss, single ended       | < 5GHz                                                                                             | 8   | 20  |      | dB    |

| Total Harmonic Distortion (THD)        | 0.1GHz sinusoidal input; ER = 6.5dB;<br>current 100μA pp - 600μA pp                                |     |     | 2    | %     |

| Total Harmonic Distortion (THD)        | 0.1GHz sinusoidal input; ER = 6.5dB;<br>current = 0.75 - 2mApp                                     |     |     | 6.5  | %     |

| Gain flatness <sup>1</sup>             | 100MHz - 5GHz; flatness referred to<br>100MHz; Input current ≤ 150µApp                             |     |     | ±1.5 | dB    |

| Deterministic jitter <sup>1</sup>      | 2 <sup>7</sup> -1 PRBS; input current 2mApp, 5dB extinction ratio                                  |     | 50  | 100  | mUlpp |

| AGC settling time                      | Within 10% of final value                                                                          |     |     | 40   | μs    |

| RSSI Accuracy                          | AC input current 150µA to 500µA                                                                    |     |     | 30   | %     |

| RSSI response time                     |                                                                                                    |     |     | 40   | ms    |

Notes:

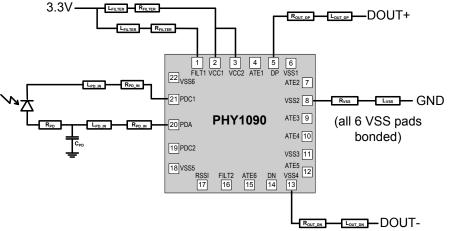

1 Using the circuit below for PD and bonding parameters (Figure 3) :

$$\label{eq:RPD} \begin{split} &\mathsf{R}_{PD} = 15\Omega; \\ &\mathsf{R}_{PD\_IN} = 500 \mathrm{m}\Omega; \\ &\mathsf{R}_{OUT\_DP/DN} = 250 \mathrm{m}\Omega; \\ &\mathsf{R}_{FILTER} = 250 \mathrm{m}\Omega; \\ &\mathsf{R}_{VCC} = 300 \mathrm{m}\Omega; \\ &\mathsf{R}_{VSS} = 100 \mathrm{m}\Omega \end{split}$$

- PD parasitics

- PDA bond wire parasitics

- DP/DN bond wire parasitics - FILT bond wire parasitics

- Combined Vcc bond wire parasitics

- Combined Vss bond wire parasitics

Figure 3: Photodiode and bonding parameters

### 4. Device Description

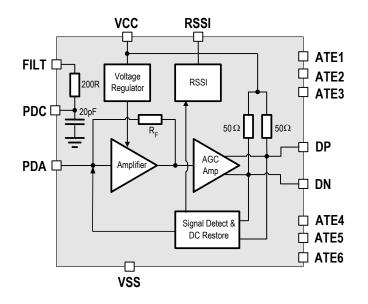

Figure 4: PHY1090 TIA block diagram

The PHY1090 is a Transimpedance Amplifier (TIA) designed for 10GBASE-LRM applications. It provides typical measured average power sensitivity for a ROSA featuring the PHY1090 of better than -18.5dBm at 10.3125Gbps. This is based upon a back-to-back link and under the conditions specified in Notes 1 and 2 of the Parametric Performance section. Since sensitivity is strongly dependant upon both the photo detector's capacitance and responsivity and individual ROSA design and bonding, this typical measured sensitivity is for illustrative purposes only.

### 4.1 Photodiode Cathode Supply

The photodiode (PD) cathode power supply is connected externally. A 20pF capacitor and  $200\Omega$  resistor are integrated into the PHY1090 to reduce cost of the ROSA, though additional decoupling within the ROSA may still be used.

The pad layout of the PHY1090 has been optimized for direct connection of the PD cathode (via the FILT pin) to Vcc. Alternatively, the pad layout also enables a PD cathode connection to a supply voltage external to the ROSA.

#### 4.2 Transimpedance & AGC Stages

The transimpedance (current to voltage) amplifier (TIA) stage is a very low noise amplifier with a feedback resistor to set the gain. An internal voltage regulator with integrated stability components is used to power the front-end TIA in order to improve the rejection of power supply noise.

The AGC stage features automatic gain control, whereby the gain is adjusted to maintain a fixed output swing. This allows the output gain to remain linear over a wide range of input signal levels.

The PHY1090 AGC gain control is a function of the peak input signal amplitude, not average input signal and has been optimized for dispersed input data.

For the purposes of test evaluation, the effect of dispersion has been emulated in the electrical domain by filtering the input data to the PHY1090 using a 4th order Bessel-Thompson filter having a 2.25GHz bandwidth. This ensures sufficient eye closure to emulate the effects of dispersion, and hence ensure correct operation of the PHY1090 AGC. In this case, 300mVpp differential typical output swing will result. If a back-to-back test is performed without any filtering or dispersion, the measured output swing is typically 200mVppd.

The TIA output features a differential supply referenced voltage amplifier, and has  $50\Omega$  single ended output impedance. For optimum supply-noise rejection, the PHY1090 should be terminated differentially.

PHY1090-RD-1.3

**Released Datasheet**

Figure 5: PHY1090 output voltage characteristic (filtered data)

#### 4.3 DC Restore

The direct-current cancellation uses low frequency feedback to remove the DC component of the input signal. This has the effect of minimizing pulse-width distortions for signals with a 50% mark density. The DC cancellation circuit is internally compensated, and does not require any additional external capacitors.

#### 4.4 RSSI

The PHY1090 RSSI output is designed to produce an OMA-based power indication *proportional* to input OMA. This can be used to generate a Loss of Signal indicator when used with a threshold detector as provided in the PHY2060 EDC enabled 10Gbps receiver.

The RSSI detector has been designed to be most accurate from  $150\mu$ App to  $500\mu$ A, to allow the detection of a valid 10GBASE-LRM signal. In this range the output RSSI current is equal to 3X the input current.

The RSSI output is referenced to V<sub>cc</sub>. When used in conjunction with Phyworks' PHY2060EDC IC, it is recommended that the RSSI current is connected to a ground (V<sub>ss</sub>) referenced 1k $\Omega$  resistor to generate a voltage indication that increases with increasing input OMA.

## 5. Typical Application Information

#### 5.1 Bonding and Layout

In order to achieve optimal ROSA performance, it is necessary to minimise noise pickup and the effects of parasitic components related to the TIA bond-out. To this end, it is recommended that:

- All bond wire lengths should be kept to a minimum, especially supply and ground wires, to minimize inductive effects.

- Bond wires carrying high speed signals be kept orthogonal to supply and ground bond wires to minimize performance degradation through pick-up.

- > The positive supply inside the ROSA should be decoupled with a good quality capacitor.

- If external PD bias is implemented, the PD bias pin should be decoupled inside the ROSA with a good quality capacitor.

- > The PD capacitance should not exceed 0.3pF to minimize degradation of bandwidth and noise.

- Bond ball should be centred and within the bond pad opening and should not occupy more than 75% of the bond pad area

- > Bond pressure of 20-25g is recommended, with a maximum ultrasonic power of 70mW for 20ms

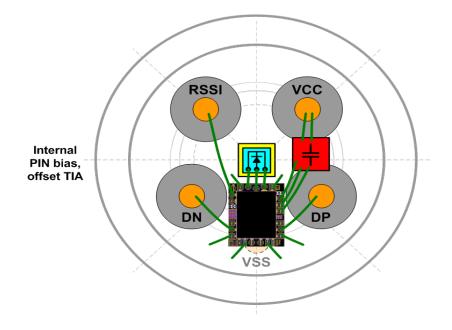

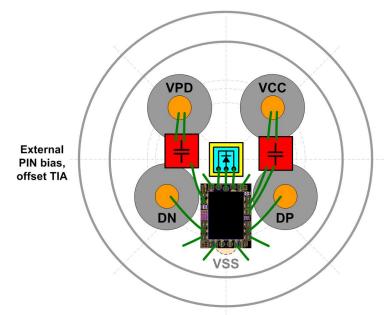

Figures 6 and 7 depict suggested bond-outs.

Note: Whilst the PHY1090 AC performance has been characterized for the bonding and PD parasitics stated in Note 2 of the Parametric Performance section, improvements in ROSA electrical bandwidth *may* be obtained by 'tuning' the bond wire length between the PD anode pad and TIA PDA pad. However, this may also adversely affect jitter and gain flatness performance.

#### 5.2 MSA Compatibility

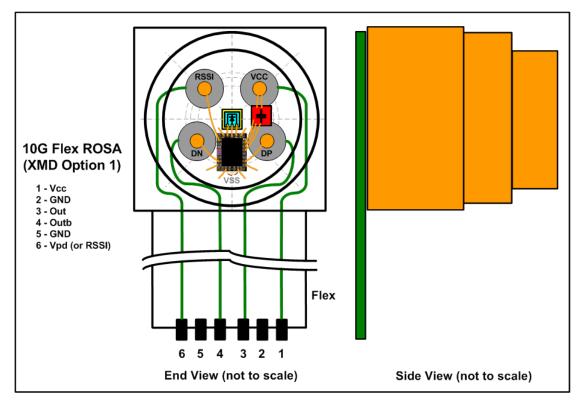

Figure 8 shows the PHY1090's compatibility with the XMD ROSA specification. Note that pin 6 of the ROSA flex can be the RSSI output from the PHY1090, or the photodiode bias voltage in the case of external bias configuration.

Figure 6: Example 5-pin TO-46 bond-out – internal PD bias (Top-view: looking into the header)

#### PHY1090-RD-1.3

Figure 7: Example 5-pin TO-46 bond-out – external PD bias (Top-view: looking into the header)

| Suggested Vcc decoupling capacitor value: | ≥470pF |

|-------------------------------------------|--------|

| Suggested Vpd decoupling capacitor value: | ≥200pF |

Figure 8: Example Flex-based ROSA

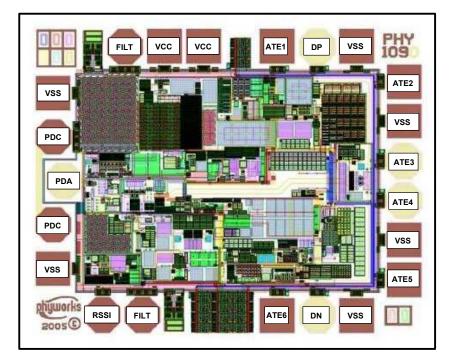

## 6. Die image, Pad Positions and Sizes

Die size: 1.169mm x 0.929mm

Thickness: 290µm +/-10µm

| Pin<br>Number | Pin Name |                          | Χ (μm) | Υ (μm) |

|---------------|----------|--------------------------|--------|--------|

| 1             | FILT1    | 80μm x 80μm, octagonal   | -258.9 | 339.5  |

| 2             | VCC1     | 80µm x 80µm, rectangular | -159.5 | 339.5  |

| 3             | VCC2     | 80µm x 80µm, rectangular | -61.5  | 339.5  |

| 4             | ATE1     | 80µm x 80µm, rectangular | 122.5  | 339.5  |

| 5             | DP       | 80µm x 80µm, octagonal   | 222    | 339.5  |

| 6             | VSS1     | 80µm x 80µm, rectangular | 321.5  | 339.5  |

| 7             | ATE2     | 80µm x 80µm, rectangular | 439.5  | 250    |

| 8             | VSS2     | 80µm x 80µm, octagonal   | 439.5  | 150    |

| 9             | ATE3     | 80µm x 80µm, octagonal   | 439.5  | 47.5   |

| 10            | ATE4     | 80µm x 80µm, octagonal   | 439.5  | -52.45 |

| 11            | VSS3     | 80µm x 80µm, rectangular | 439.5  | -150   |

| 12            | ATE5     | 80µm x 80µm, rectangular | 439.5  | -250   |

| 13            | VSS4     | 80µm x 80µm, rectangular | 321.5  | -339.5 |

| 14            | DN       | 80µm x 80µm, octagonal   | 222    | -339.5 |

| 15            | ATE6     | 80µm x 80µm, rectangular | 121.6  | -339.5 |

| 16            | FILT2    | 80µm x 80µm, octagonal   | -215   | -339.5 |

| 17            | RSSI     | 80µm x 80µm, octagonal   | -315   | -339.5 |

PHY1090-RD-1.3

**Released Datasheet**

| 18 | VSS5 | 80µm x 80µm, rectangular | -439.5 | -221.5 |

|----|------|--------------------------|--------|--------|

| 19 | PDC1 | 80µm x 80µm, octagonal   | -439.5 | -110.5 |

| 20 | PDA  | 80µm x 80µm, octagonal   | -439.5 | 0      |

| 21 | PDC2 | 80µm x 80µm, octagonal   | -439.5 | 110.75 |

| 22 | VSS6 | 80µm x 80µm, rectangular | -439.5 | 221.5  |

### **Contact Information**

For technical support, contact Maxim at www.maximintegrated.com/support.

#### Disclaimer

This datasheet contains preliminary information and is subject to change.

This document does not transfer or license any intellectual property rights to the user. It does not imply any commitment to produce the device described and is intended as a proposal for a new device.

Phyworks Ltd assumes no liability or warranty for infringement of patent, copyright or other intellectual property rights through the use of this product.

Phyworks Ltd assumes no liability for fitness for particular use or claims arising from sale or use of its products.

Phyworks Ltd products are not intended for use in life critical or sustaining applications.