Integrated CMOS Colour Image Sensor with on-chip ADC.

#### **Key Features**

- Standard image format: 160 x 120

- 164 x 124 Bayer Patern colour pixel array

- Variable frame rate (< 0.3 f/s 60 f/s)

- On-chip 8-bit A/D convertor

- 8-bit and 4-bit conversion modes

- 8-wire and 4-wire parallel data output modes

- Reduced flicker operation with 50Hz and 60Hz mains frequencies

#### **GENERAL DESCRIPTION**

VV6300 is a highly-integrated CMOS image sensing device. In addition to a 160 x 120 pixel image sensor array, the device includes on-chip circuitry to drive and sense the array.

The output stage of the sensor contains a successive approximation circuit which performs analogue-todigital conversion of the photodiode array to produce 8-bit or 4-bit pixel data.

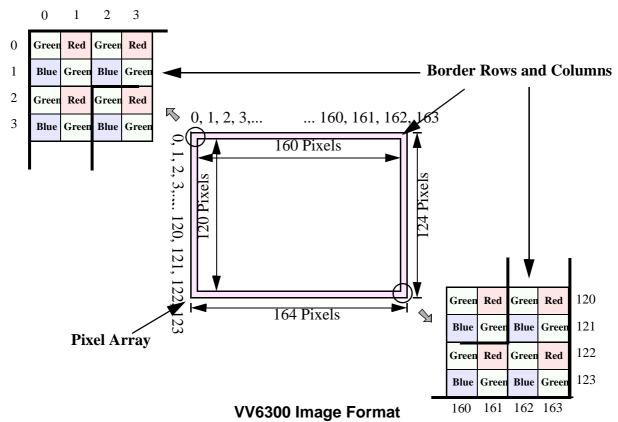

The primary image size is  $160 \times 120$  but border pixels/lines can be enabled to give an effective image size of  $164 \times 124$ .

Automatic exposure and gain controller

2 serial data output modes

- Automatic black level calibration

- Options selectable via serial interface

- Configuration Autoload from E<sup>2</sup>Prom

- Evaluation Kit available (See seperate datasheet)

VV6300 features electronic exposure and gain control over a wide range, enabling the use of a single fixed-aperture lens.

A bi-directional 2-wire serial communications interface allows the device to be configured and its operating status monitored. The status information may also be multiplexed onto the digital output bus.

# NB. A colour processor will be required to convert the raw colourised pixel data into colour image information.

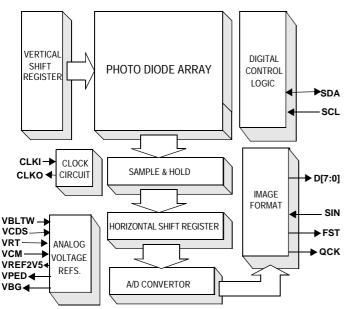

## **BLOCK DIAGRAM**

| 160 x 120           |

|---------------------|

| 12µm x 12µm         |

| 1.92mm x 1.44mm     |

| 5v +/-10%           |

| 5 Lux               |

| 175 mW (Typ.)       |

| 36 dB (Typ.)        |

| Automatic (25000:1) |

| -20°C to +70°C      |

| Ceramic 48LCC       |

|                     |

#### **Main Features**

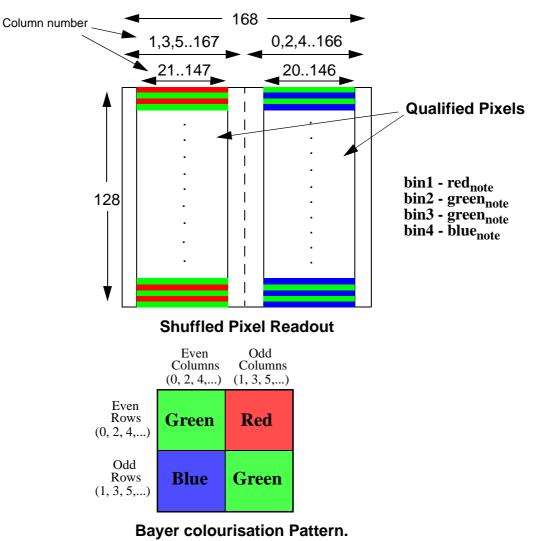

Bayer pattern colour array with default image format of 160 x 120. Extra border pixel/lines can be enabled to give an image size of 164 x 124. Shuffled read out to reduce pixel crosstalk. Digital pixel data coding assigns  $10_{\rm H}$  as black and F0<sub>H</sub> as white. Other codes specify line sync and frame sync periods.

On-chip 8-bit successive approximation analogue-to-digital convertor with 8-wire, 4-wire parallel and two serial data output modes.

The VV6300 frame rates can be integer multiples of the mains supply frequencies used worldwide, i.e. 50Hz and 60Hz. This ensures reduced flicker operation of the sensor

All VV6300 operating modes and system status information can be accessed via a two wire bidirectional serial interface.

VV6300 features an automatic electronic exposure algorithm that enables the use of a single fixed-aperture lens. Automatic gain control enhances operation under low light conditions.

Automatic black level control ensures consistent picture quality across the whole range of operating conditions. Extensive use of automated operation and on chip references means that only a small number of passive components are needed to realise a complete video camera.

On-chip voltage references simplifies the support circuitry and maintains device stability over a wide range of operating conditions.

#### Exposure Control

With automatic exposure control selected VV6300 uses a complex algorithm to automatically set the exposure value for the current scene. When combined with clock control and gain control the VV6300 can operate over a very wide range of illumination levels.

Where direct control of the exposure is required the exposure value can be directly selected by writing to the appropriate registers via the serial interface.

#### **Clock Control**

The system clock can be divided down internally to extend the operating range of VV6300 by allowing longer exposure times. The clock divisor can be varied from 1 to 8 in times two steps i.e there are 4 different values. Note: changing the system clock divisor modifies the pixel and frame rate.

#### Gain Control

If the image is to dark and the exposure is already close to its maximum, VV6300 will increase the system gain.

Gain can be varied from x1 to x8 in times two steps i.e there are 4 different gain settings. If the scene is too dark and integration period has almost reached its maximum value the gain value is incremented by one step (i.e. doubled). If the gain setting changes the exposure value is automatically set to half the maximum integration period. The exposure controller then increases the exposure value as necessary.

Similarly if the image is too bright and the integration period is short then gain will be reduced by one step (i.e. divide by two). As before, the exposure value is set to half the maximum integration period. The exposure controller can then adjust the exposure value as necessary to provide a correctly exposed image.

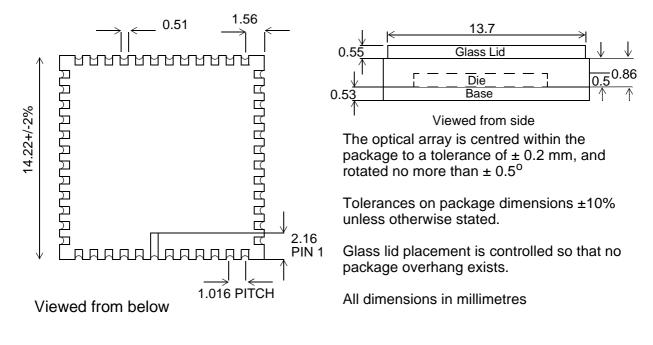

## **Package Details**

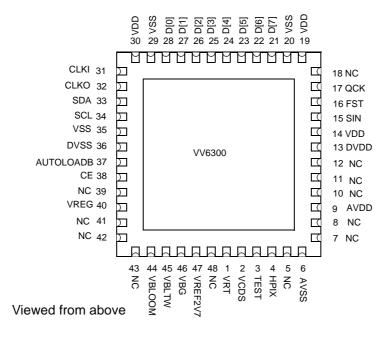

### **Device Pinout**

## **Pin Function List**

| Pin   | Name          | Туре | Description                                                            |

|-------|---------------|------|------------------------------------------------------------------------|

|       |               |      | POWER SUPPLIES                                                         |

| 6     | AVSS          | GND  | Analogue ground                                                        |

| 9     | AVDD          | PWR  | Analogue power                                                         |

| 13    | DVDD          | PWR  | Digital power                                                          |

| 14    | VDD           | PWR  | Power                                                                  |

| 19    | VDD           | PWR  | Power                                                                  |

| 20    | VSS           | GND  | Ground                                                                 |

| 29    | VSS           | GND  | Ground                                                                 |

| 30    | VDD           | PWR  | Power                                                                  |

| 35    | VSS           | GND  | Ground                                                                 |

| 36    | DVSS          | GND  | Ground                                                                 |

|       |               |      | ANALOGUE OUTPUTS                                                       |

| 1     | VRT           | IA   | Pixel reset voltage                                                    |

| 2     | VCDS          | IA   | Voltage reference                                                      |

| 3     | TEST          | IA   | Analogue test                                                          |

| 40    | VREG          | IA   | Reference voltage input                                                |

| 44    | VBLOOM        | OA   | Internal reference voltage                                             |

| 45    | VBLTW         | IA   | Bitline test white reference                                           |

| 46    | VBG           | OA   | Internally generated bangap reference voltage 1.22V                    |

| 47    | VREF2V5       | OA   | Internally generated reference voltage 2.5V                            |

|       |               |      | DIGITAL OUTPUTS                                                        |

| 16    | FST           | OD   | Frame start. Synchronises external image capture.                      |

| 17    | QCK           | OD   | Pixel sample clock. Qualifies video output for external image capture. |

| 25-28 | D[3:0]        | BI↓  | Parallel 4-bit databus. D[0] serial data bus.                          |

| 21-24 | D[7:4]        | OD↓  | Parallel 4-bit databus.                                                |

|       |               | D    | IGITAL CONTROL SIGNALS                                                 |

| 34    | SCL           | BI↑  | Serial bus clock (bidirectional, open drain)                           |

| 33    | SDA           | BI↑  | Serial bus data (bidirectional, open drain)                            |

| 37    | AUTOLO<br>ADB | ID↓  | Enable autoload from EEPROM                                            |

| 38    | CE            | ID↑  | Chip enable                                                            |

| 4     | HPIX          | ID↓  | Hold pixel value.                                                      |

| 15    | SIN           | ID↓  | Frame Timing reset(Soft reset)                                         |

|       |               |      | SYSTEM CLOCKS                                                          |

| 31    | CLKI          | ID   | Oscillator input.                                                      |

| 32    | CLKO          | OD   | Oscillator output.                                                     |

OA - Analogue output OD - Digital output BI - Bidirectional  $OD\downarrow$  – Digital output with internal pull-down

A - Analogue input D - Digital input ID↑ – Digital input with internal pull-up

## SPECIFICATIONS

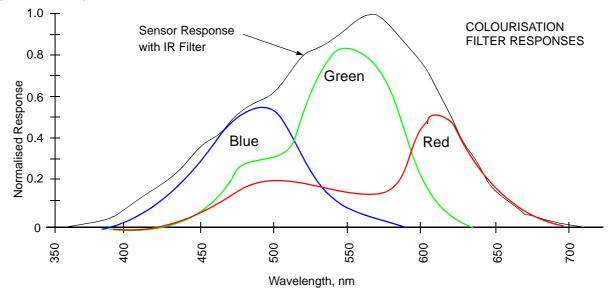

## **Spectral Response**

## **Absolute Maximum Ratings**

| Parameter                               | Value                                         |

|-----------------------------------------|-----------------------------------------------|

| Supply Voltage                          | -0.5 to +7.0 volts                            |

| Voltage on other input pins             | -0.5 to V <sub>DD</sub> + 0.5 volts           |

| Temperature under bias                  | -15°C to 85°C                                 |

| Storage Temperature                     | -30°C to 125°C                                |

| Maximum DC TTL output Current Magnitude | 10mA (per o/p, one at a time, 1sec. duration) |

Note: Stresses exceeding the Absolute Maximum Ratings may induce failure. Exposure to absolute maximum ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

## **DC Operating Conditions**

| Symbol          | Parameter                     | Min. | Тур. | Max.                 | Units | Notes     |

|-----------------|-------------------------------|------|------|----------------------|-------|-----------|

| V <sub>DD</sub> | Operating supply voltage      | 4.75 | 5.0  | 5.25                 | Volts |           |

| V <sub>IH</sub> | Input Voltage Logic "1"       | 2.4  |      | V <sub>DD</sub> +0.5 | Volts |           |

| V <sub>IL</sub> | Input Voltage Logic "0"       | -0.5 |      | 0.8                  | Volts |           |

| T <sub>A</sub>  | Ambient Operating Temperature | -20  |      | 70                   | °C    | Still air |

## AC Operating Conditions

| Symbol | Parameter         | Min. | Тур.   | Max. | Units | Notes |

|--------|-------------------|------|--------|------|-------|-------|

| CKIN   | Crystal frequency |      | 14.318 |      | MHz   | 1     |

| SCL    | Serial Data Clock |      |        | 100  | KHz   | 2     |

- 1. Pixel Clock =  $^{CKIN}/_{2}$

- 2. Serial Interface clock must be generated by host processor.

## **Electrical Characteristics**

| Symbol              | Parameter                  | Min. | Тур.  | Max. | Units | Notes                       |

|---------------------|----------------------------|------|-------|------|-------|-----------------------------|

| I <sub>DCC</sub>    | Digital supply current     |      | 10    |      | mA    | 1                           |

| I <sub>ADD</sub>    | Analog supply current      |      | 25    |      | mA    | 1                           |

| I <sub>DD</sub>     | Overall supply current     |      | 35    |      | mA    | 1                           |

| V <sub>REF2V7</sub> | Internal voltage reference |      | 2.700 |      | Volts |                             |

| V <sub>BG</sub>     | Internal bandgap reference |      | 1.22  |      | Volts |                             |

| V <sub>OH</sub>     | Output Voltage Logic "1"   | 2.4  |       |      | Volts | I <sub>OH</sub> = 2mA       |

| V <sub>OL</sub>     | Output Voltage Logic "0"   |      |       | 0.6  | Volts | I <sub>OL</sub> = -2mA      |

| I <sub>ILK</sub>    | Input Leakage current      | -1   |       |      | μΑ    | V <sub>IH</sub> on<br>input |

|                     |                            |      |       | 1    | μΑ    | V <sub>IL</sub> on<br>input |

Typical conditions,  $V_{DD} = 5.0 \text{ V}$ ,  $T_A = 27^{\circ}\text{C}$

1. Digital and Analogue outputs unloaded - add output current.

## **Operating Characteristics**

| Parameter           | min. | typ. | max. | units     | Note                                                                                                                                                                        |

|---------------------|------|------|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dark Current Signal |      | 50   |      | mV/Sec    | Modal pixel voltage due to photodiode leak-<br>age under zero illumination with Gain=1<br>$(V_{dark} = (V_{t1} - V_{t2})/(t1-t2)$ , calculated over<br>two different frames |

| Sensitivity         |      | 6    |      | V/Lux-Sec | V <sub>Ave</sub> /Lux·10ms, where Lux gives 50% satu-<br>ration with Gain=1 and Exposure=10ms                                                                               |

| Min. Illumination   |      | 10   |      | Lux       |                                                                                                                                                                             |

| Shading             |      | ТВА  |      | %         | Variance of V <sub>ave</sub> over eight equal blocks at 66% saturation level illumination                                                                                   |

| Random Noise        |      | -36  |      | dB        | RMS variance of all pixels, at 66% satura-<br>tion, over four frames                                                                                                        |

| Smear               |      | ТВА  |      | %         | Ratio of $V_{ave}$ of the area outside a rectangle 25 lines high illuminated at $500xV_{50\%}$ level to $V_{Ave}$ of the rectangle                                          |

| Flicker             |      | ТВА  |      | %         | Variation of V <sub>ave</sub> of one line from field to field<br>at 66% saturation level illumination                                                                       |

| Lag                 |      | TBA  |      | %         | Average residual signal with no illumination<br>in the field following one field of 66% sat.<br>illumination                                                                |

| Blooming            |      | ТВА  |      |           | Ratio of spot illumination level that produces $0.1xV_{sat}$ output from immediately around the spot to the V <sub>sat</sub> spot illumination level (pinhole target)       |

Note: Devices are normally not 100% tested for the above characterisation parameters, other than Dark Current Signal (see Blemish Specification below).

All voltage (V<sub>A</sub>, V<sub>ave</sub>, V<sub>sat</sub>, V<sub>xx%</sub>) measurements are referenced to the black level, V<sub>black</sub>, and spot blemishes are excluded (see Blemish Specification below). V<sub>xx%</sub> refers to the output that is xx% of saturation, that is peak white

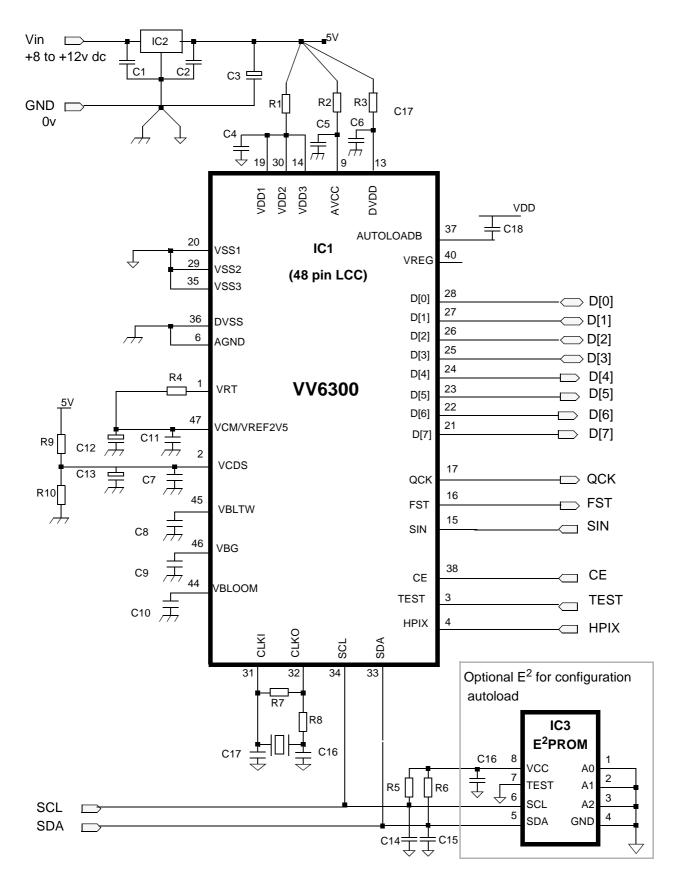

## **Test Conditions**

The sensor is tested using the example support circuit illustrated later in this document. Standard imaging conditions used for optical tests employ a tungsten halogen lamp to uniformly illuminate the sensor (to better than 0.5%), or to illuminate specific areas. A neutral density filter is used to control the level of illumination where required.

| Illumination Colour Temp. | 3200 <sup>o</sup> K |

|---------------------------|---------------------|

| Clock Frequency           | 14.318MHz           |

| Exposure                  | Maximum             |

| Gain                      | x1                  |

| Auto. Gain Control (AGC)  | Off                 |

## **Blemish Specification**

A Blemish is an area of pixels that produces output significantly different from its surrounding pixels for the same illumination level. The definition of a Blemish Pixel varies according to testing conditions as follows:

| Test                | Exposure  | Illumination | Blemish Pixel output definition                                                                                                                            |

|---------------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 - Black Frame     | Minimum   | Black        | Differing more than ± 100 mV. from modal value.                                                                                                            |

| 2 - Dark Current    | Maximum   | Black        | Output more than three times the modal value (see Dark Current Signal above).                                                                              |

| 3 - Pixel Variation | Mid range | 66% Sat.     | Differing more than $\pm 35$ mV from modal value.<br>Note: The mode of pixel values must be within $\pm 70$ mV of 66% of V <sub>sat</sub> for all devices. |

Note: Gain is set to Minimum and Correction set to Linear for all tests; measurement of blemishes for Test 3 is conducted under standard illumination (see above), set to produce average output of 66% saturation level.

The blemish specification is then defined as follows:

| Max. No. of Blemishes | Notes                                     |

|-----------------------|-------------------------------------------|

| 4                     | Unconnected single pixels                 |

| 1                     | Of up to four connected pixels (2x2 max.) |

NB, pixel blemishes may occur anywhere on the array.

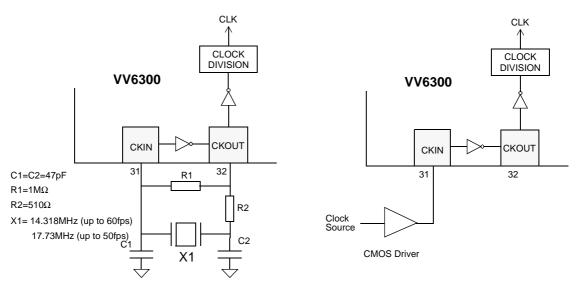

#### **System Clock Generation**

VV6300 generates a system clock when a quartz crystal or ceramic resonator circuit is connected to the CLKI and CLKO pins. The device can also be driven directly from an external clock source driving CLKI.

#### **Camera Clock Source**

For greater flexibility the input frequency can be divided by 1, 2, 4 or 8 to select the pixel clock frequency. Two bits in the clock division register in the serial interface select the input clock frequency divisor. The table below gives the different frame rates that can be selected, when CLKI = 14.318MHz, for each divisor. The default clock divisor setting is a divide by 2. To achieve maximum frame rates data is converted at 4 bit resolution.

| CLKI<br>(MHz) |   |   | Divisor | Pixel Freq.<br>(kHz) | Frame rate <sup>1</sup> (fps) | Comments |

|---------------|---|---|---------|----------------------|-------------------------------|----------|

| 14.318        | 0 | 0 | 1       | 1790                 | 59.98                         | default  |

| 14.318        | 0 | 1 | 2       | 895                  | 29.99                         |          |

| 14.318        | 1 | 0 | 4       | 448                  | 15.01                         |          |

| 14.318        | 1 | 1 | 8       | 224                  | 7.5                           |          |

#### Clock Division (60Hz Video Mode)

1. Approximate frame rate. Assumes 160 x 120 image format, parallel data output and 4 bit data conversion

#### Image Format

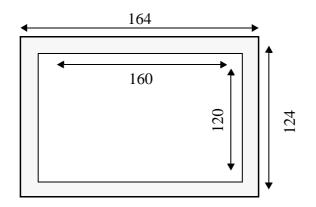

VV6300 has a single output image size, 160 x 120 pixel. The image size can be modified by asserting the "enable borders" serial interface register bit, (Setup1,  $[001_0001_2]$ ). The extended image size is 164 x 124 pixels. The default image format is 160 pixels by 120 lines.

| Enable borders | Image size (column x row) | Comment |

|----------------|---------------------------|---------|

| 0              | 160 x 120                 | default |

| 1              | 164 x 124                 |         |

### **Image Format Selection**

The diagram below shows the relationship between the default 160 x 120 pixel image and the extended 164 x 124 pixel format. A border, 2 pixels wide is enabled around the basic array.

**Output Image Dimensions**

#### Frame Timing

The VV6300 frame rate depends upon:

- (i) the frequency of the system clock (CLKI)

- (ii) the ADC conversion accuracy (8-bit or 4-bit)

- (iii) the internal clock divisor selected (1, 2, 4, or 8)

- (iv) the output format selected (8-wire, 4-wire, serial or UART)

User can set their own values for CLKI, the ADC conversion rate and also the clock divisor setting, subject to achieving a frame rate up to 60 frames/sec.

The frame rate is determined in the following way:

An example is given with a clock input of 14.318MHz, 160 x120 image format, 8-bit ADC conversion rate and a clock divisor of 2.

- 1. Determine clock input (CLKI) frequency 14.318MHz

- 2. Pixel period = (divisor x conversion factor x output format factor) / CLKI

| Clock divisor     | =       | 1, 2, 4 or 8.                                               |

|-------------------|---------|-------------------------------------------------------------|

| Conversion factor |         | 8 for 8-bit ADC accuracy                                    |

|                   | =       | 4 for 4-bit ADC accuracy                                    |

| Output format fac | tor =   | 2 for 8-wire, 4-wire, serial output modes                   |

|                   | =       | 6 for UART mode                                             |

|                   |         |                                                             |

| Example: Piz      | xel per | riod = $(2 \times 8 \times 2) / 14.318$ MHz = 2.235 $\mu$ s |

3. Line period = (no. of visible pixels + line overhead) x pixel period

The number of visible pixels per line is 160. The interline pixel period overhead (including the 4 border pixels that can be enabled to qualify extra video information) is mode dependent, 43 pixel periods for 60Hz mode or 141 pixel periods for 50Hz mode.

Example: Line period = (160 + 43) x 2.235µs = **453.705**µs

4. Frame period = (no. of visible lines + frame overhead) x line period

For the purposes of calculating the effective frame rate the number of active lines is assumed to be fixed at 120. The frame overhead (which includes the 4 border lines that can be enabled to qualify extra video information) has a constant value of 27 line periods.

| Example: | Frame period | = (120 + 27) x 453.705µs | = 66.694ms             |

|----------|--------------|--------------------------|------------------------|

|          | Frame rate   | = 1 / frame period       | = 15 frames per second |

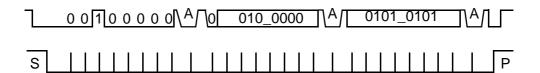

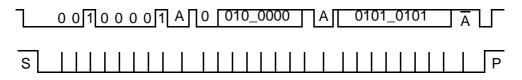

### **Digital Data Output Modes**

VV6300 provides several different output modes. The different data formats are selected via the appropriate register in the serial interface, Setup0,  $[001_0000_2]$ , bits 5 and 6. 8-bit or 4-bit pixel data conversion is also selected via the serial interface, Setup1,  $[001_0001_2]$ . If 4-bit pixel data conversion is selected as well as 8-Wire parallel output format then 2 consecutive pixel nibbles may be packed into a single output byte therefore increasing the effective frame rate.

| Setup<br>Bit 6 | Setup<br>Bit 5 | Description     | Comment |

|----------------|----------------|-----------------|---------|

| 0              | 0              | 8-Wire Parallel |         |

| 0              | 1              | 4-Wire Parallel | default |

| 1              | 0              | Serial          |         |

| 1              | 1              | Serial UART     |         |

**Data Output Modes**

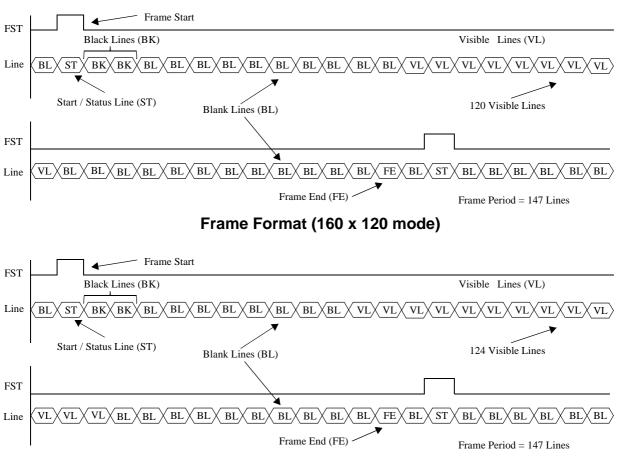

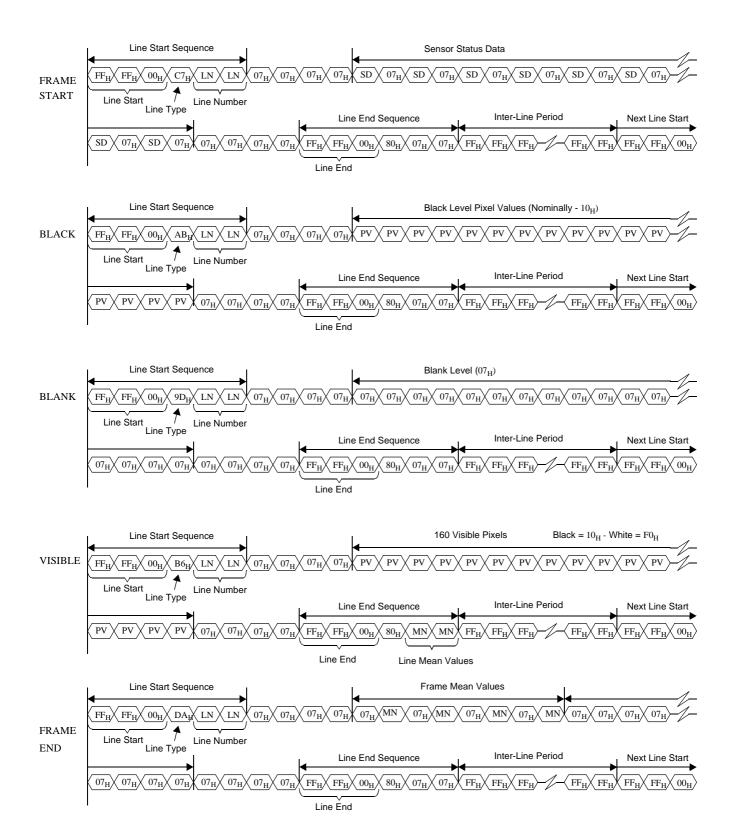

## Frame Level Formatting

The frame level format for each mode is common and is given below. FST can be used for frame synchronisation. The FST pulse is exactly one line period in length and the rising edge occurs just before the status line start sequence (see line level formatting) is output.

Frame Format (164 x 124 mode)

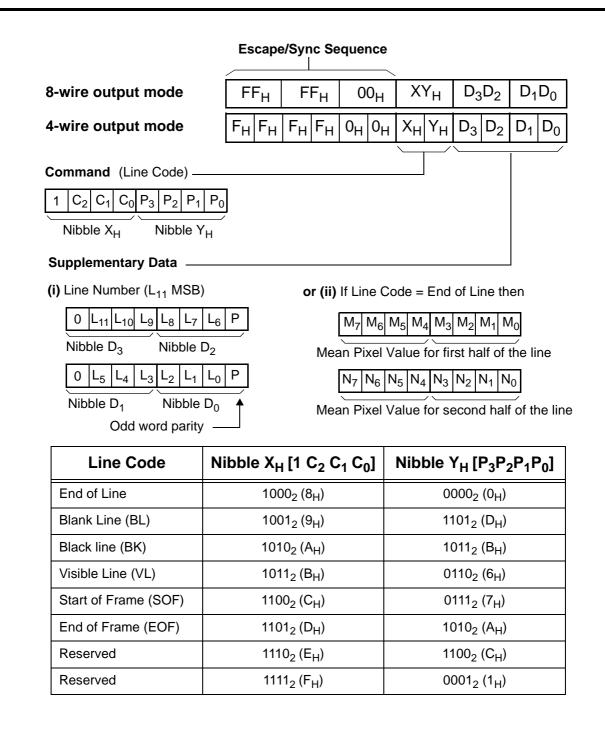

## Line Level Formatting

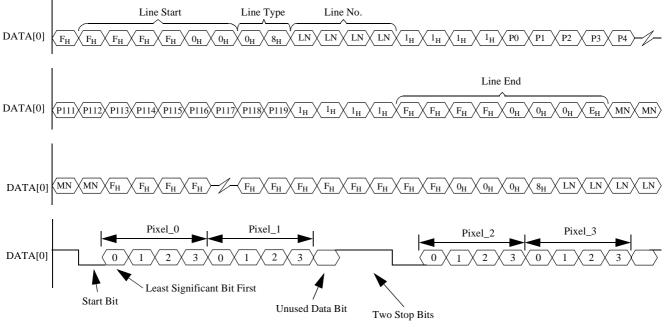

Each line type (black, blank, visible) has a specific format associated with it independent of the data output format selected. Each line begins with a start sequence of FF<sub>H</sub> FF<sub>H</sub> 00<sub>H</sub> followed by XY<sub>H</sub> where XY<sub>H</sub> indicates the line type. The next two bytes provide supplementary data (specifically the line number within the current frame). Following this data are two guaranteed blank bytes (07<sub>H</sub> 07<sub>H</sub> for 8 bit modes, 01<sub>H</sub> 01<sub>H</sub> for 4 bit modes). If the border lines/pixels have been enabled the next 2 bytes will be visible pixels otherwise they shall appear as blank bytes. The next part of the line is reserved for the 160 visible pixels. The 4 bytes following the visible pixels are formatted in the same way as the 4 bytes preceeding the 160 visible pixels. At the end of each line, an end of line sequence is produced, (FF<sub>H</sub> FF<sub>H</sub>  $00_H 80_H$ ). If the line is within the visible part of the frame, (lines 11 to 134 if the border lines are enabled otherwise lines 13 to 132), the end of line sequence is immediately followed by 2 bytes containing the mean values for the central 128 pixels. The first byte contains the mean value for the first 64 pixels of the middle 128 pixels and the second byte contains the mean value for the latter 64 pixels of the middle 128 pixels. The 128 pixels comprise the standard 120 visible pixels, the 4 border pixels and an extra 4 border pixels that are never enabled as visible pixels but are used for exposure control and hence contribute to the mean pixel value for the line. If the line type is not visible then the two bytes following the end of line sequence will contain 07<sub>H</sub> 07<sub>H</sub>. For the remainder of the interline period the data output is always FF<sub>H</sub>.

Sensor status and configuration information is output during the frame start line, (line 0), each data byte is separated by a blank value  $(07_{\rm H})$  to avoid possible false line start conditions being generated. The information output during the status line reflects, if the sensor is operating in 8bit ADC mode, the first 64 locations in the serial interface register map. If the sensor is operating in 4 bit mode less data can be output during the status line. All the serial interface registers are 8bit values therefore 2, 4bit pixel periods are required to output a single serial interface location. Note that the serial interface data is only output during the visible monochrome pixels of the status line. This allows for one quarter of the serial interface address space to be output during any status line. It is possible to select the remaining registers in the serial interface for output, (see serial interface register setup 2, bits 7:6).

The "end of frame" line, it is actually 2 lines prior to the status line will output the 4 exposure control bin averages during the first 4, (or 8 if operating in 4bit modes) monochrome pixels. Again the data is separated by mode dependent padding data.

#### VV6300 Sensor

Line Coding

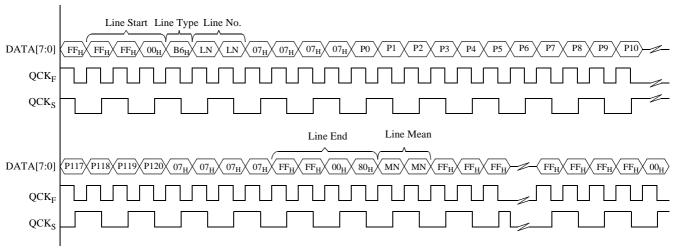

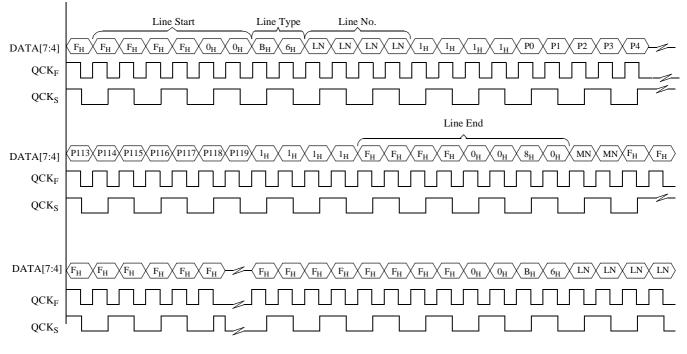

#### 8-Wire Parallel Mode

8-Wire parallel mode is selected when the appropriate bits are set via the serial interface.

When 8-bit conversion mode is selected the 8-bit pixel data is output on pins DATA[7:0]. The start of a frame is indicated by a pulse on FST. The data is valid on the falling edge of the pixel sample clock fast QCK ( $QCK_F$ ) or on each edge of the slow QCK ( $QCK_S$ ).

#### 8-Wire Parallel Mode (8-bit Pixel Data)

When 4-bit conversion mode is selected the 4-bit pixel data is output two bytes at a time on the DATA[7:0] pins. The first pixel is mapped onto DATA[7:4] and the second pixel is output on DATA[3:0]. This effectively doubles the pixel rate (and halves the frame period).

## 8-Wire Parallel Mode (4-bit Pixel Data)

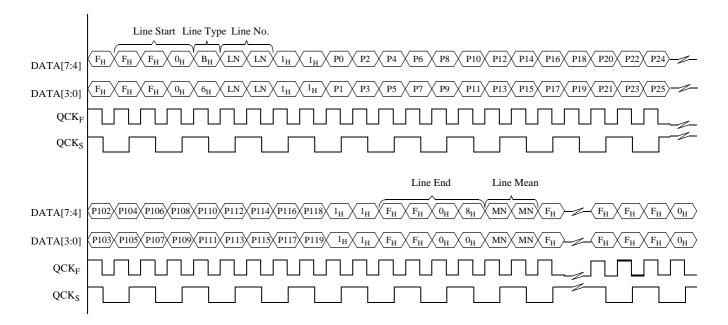

#### **4-Wire Parallel Mode**

4-Wire parallel mode is selected when the appropriate bits are set via the serial interface. When 8-bit data conversion mode is selected (CONV8 = 1) the 8-bit pixel data is output on pins DATA[7:4] in two 4-bit nibbles. The start of a frame is indicated by a pulse on FST. A QCK sample edge is generated for each nibble.

4-Wire Parallel Mode (8-bit Pixel Data)

When 4-bit data conversion mode is selected (CONV8 = 0) the 4-bit pixel data is output on pins DATA[7:4].

4-Wire Parallel Mode (4-bit Pixel Data)

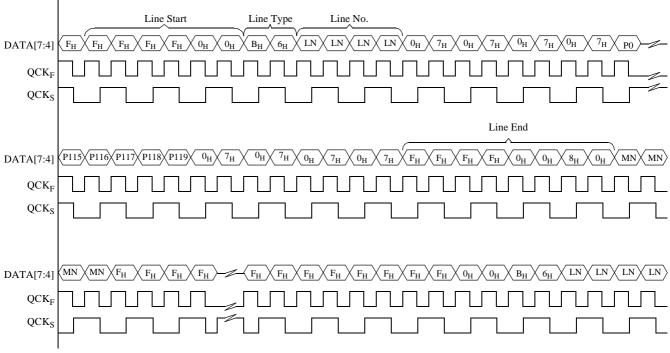

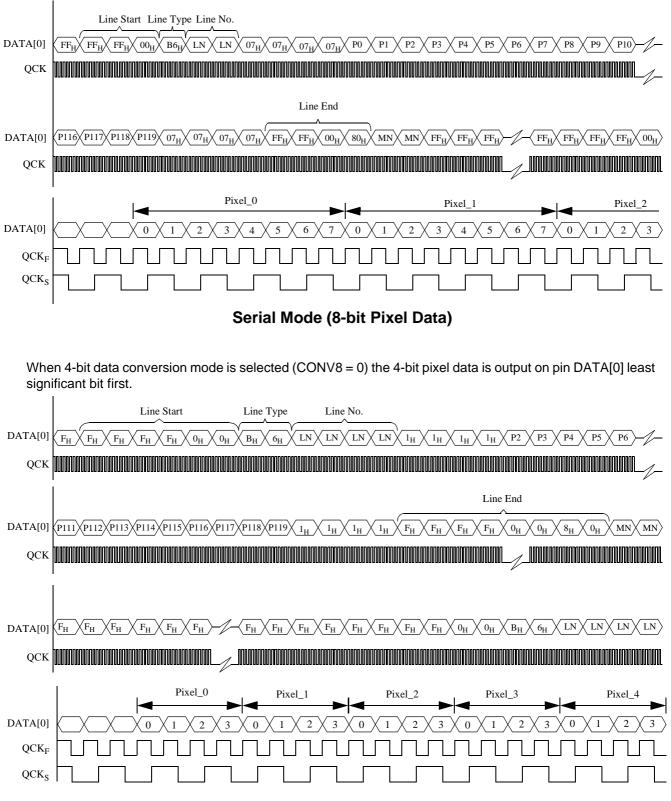

### **Serial Mode**

Serial mode is selected when the appropriate bits are set via the serial interface. When 8-bit data conversion mode is selected the 8-bit pixel data is output on pin DATA[0] least significant bit first.

Serial Mode (4-bit Pixel Data)

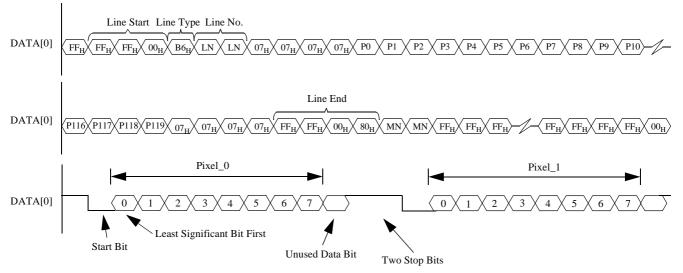

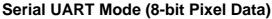

### Serial UART Mode

Serial UART mode is selected when the appropriate bits are set via the serial interface. When 8-bit data conversion mode is selected the 8-bit pixel data is output on pin DATA[0] least significant bit first. Each pixel is preceded by a start bit and followed by an additional data bit and two stop bits.

When 4-bit data conversion mode is selected the 4-bit pixel data is output two pixels at a time on pin DATA[0] least significant bit first. Each pixel is preceded by a start bit and followed by an additional data bit and two stop bits.

## Serial UART Mode (4-bit Pixel Data)

All the above output format modes assume that the sensor is operating in the default sensor read-out mode, namely, non shuffle and a monochrome image size of 160 by 120. The visible image can be increased to 164 by 124. This image size will normally be selected when operating in colour modes. The extra border of pixels is required by color processor algorithms to help with interpolation at the edge of the pixel array. The pixel

read-out is shuffled to avoid crosstalk between the color channels. The read-out order is all the odd column pixels followed by all the even column pixels.

note: if this document has **not** been reproduced on a color printer then the color assignments are as follows: left region (row numbering from 0 to 127) - red rows 0,2,4,6 etc. green rows 1,3,5,7 etc. right region (row numbering from 0 to 127) - green rows 0,2,4,6 etc. blue rows 1,3,5,7 etc.

## **Qualifying the Output Data**

Data is output from VV6300 in a continuous stream. By utilising signals, like FST, and key events, like the start of a line or the end of line, the user can sample and display the image data. QCK is used to sample the data, as described in the previous section. By default the falling edge of QCK will sample the data, however it is possible to use both the rising and falling edges of a slow QCK QCK<sub>S</sub> to sample the data.

Different sections of the frame can be enabled by QCK. The options, which are selected via setup register4 in the serial interface, are as follows, firstly the QCK can be disabled, therefore no data will be qualified. This is the default option.

The second option is to have the QCK free running where all the data is qualified.

The third option is to only qualify the image data, which also includes the 2 black calibration monitor lines, lines 1 and 2 in the frame. This option is further complicated in that extra black lines and the extra border pixels/lines can be enabled giving the following 4 options:

- 1. Black lines (1-2) plus image (160 pixels by 120 lines)

- 2. Black lines (1-8) plus image (160 pixels by 120 lines)

- 3. Black lines (1-2) plus image (164 pixels by 124 lines)

- 4. Black lines (1-8) plus image (164 pixels by 124 lines)

The final option is to qualify the embedded frame control sequences as well as the image data. These control sequences are the 6 bytes at the start and at the end of each image line, where an image line is defined above. The frame start or status line, image and control sequence pixels, will also be qualified during this mode.

#### **QCK Exceptions**

The output data from VV6300 can be formatted in many ways, as detailed in an earlier section of this document. Under certain operating conditions the relationship between QCK and the output data is compromised.

It is vital that the phase relationship between the output data stream and the QCK must be maintained from line to line, for example ensuring that, if enabled, the line code byte is always qualified by the same edge of the QCK, clearly only applicable when considering slow QCK qualification. It is known that there are an odd number of pixel periods in each line of the frame. If the slow QCK is selected then clearly two pixels are qualified during each QCK cycle resulting in the following modes of operation requiring special care: 4 bit ADC 8 wire output, 8 bit ADC 8 wire output and 4 bit ADC 4 wire output. During the interline period, when the data bus is outputting data fixed at FF (8bit ADC) or F (4bit ADC), the phase of the QCK is toggled, this will occur during every interline period. For the 8bit 8wire or 4bit 4 wire options this change is a simple inversion. The 4bit 8wire option is not quite as straightforward. During the interline period the QCK signal is changed from its former state to 1 of 3 other states. In addition 2 out of the 4 possible states are video timing mode

dependent.

Please note that the number of nibbles/bytes qualified by the clocks described above, during the free running QCK mode, will differ from the expected value, as follows:

#### **QCK Exception Details**

| Operating Mode |                  | ixels qualified per second | Number of pixels qualified<br>60 frames per second |                  |

|----------------|------------------|----------------------------|----------------------------------------------------|------------------|

|                | QCK <sub>F</sub> | QCK <sub>S</sub>           | QCK <sub>F</sub>                                   | QCK <sub>S</sub> |

| 4bit 4wire     | 203              | 202                        | 301                                                | 300              |

| 4bit 8wire     | 202              | 198                        | 300                                                | 298              |

| 8bit 8wire     | 203              | 202                        | 301                                                | 300              |

| <b>Pixel qualification exceptions</b> | ication exception | qualification | Pixel |

|---------------------------------------|-------------------|---------------|-------|

|---------------------------------------|-------------------|---------------|-------|

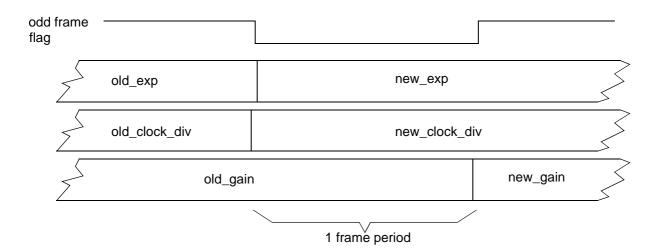

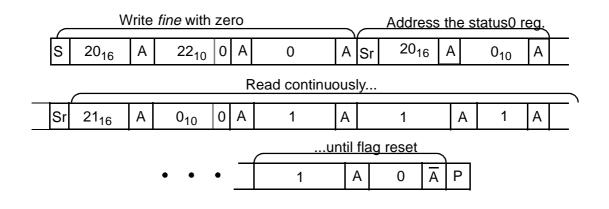

### Serial Interface - Exposure Control Handshake

The process of writing timed exposure, clock division or gain settings to VV6300 using the serial interface requires special attention. These timed parameters can be written to the serial interface at any point within the frame timing but will only be transferred from shadow registers to their active registers at a specific point within the frame timing, see diagram below. Please note that writing immediate clock division or gain parameters are treated as a "normal" serial interface write messages.

Since the new external exposure, clock division or gain settings are written to shadow registers the user continues to have full read/write access to the serial interface. A handshake system has been implemented between the exposure controller and the serial interface to avoid the user writing, for example, a second external timed gain value while the exposure controller has yet to transfer the first external timed gain value from the shadow register to the active register. If an external timed gain message has been written a special flag will be raised to indicate that it has yet to be transferred to the active register. This flag is available to the user via reading the status 0 register in the serial interface. Until the flag is lowered the user knows that it is not safe to write a further external gain value. Identical handshake protocols are used to implement timed external exposure and clock division writes.

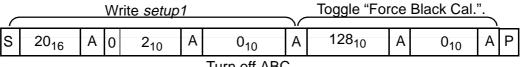

## Auto Black Calibration

Black calibration is used to remove voltage offsets that cause shifts in the black level of the video signal. VV6300 is equipped with an automatic function that continually monitors the output black level and calibrates if it has moved out of range. Black calibration can be split into two stages, **monitor** (1 cycle) and **update** (3 cycles). During the monitor phase the current black level is compared against two threshold values. If the current value falls outside the threshold window then an update cycle is triggered. The update cycle can also be triggered by a change in the gain applied to sensor core or via the serial interface.

## **Serial Interface**

In order to be controlled and configured by its host, VV6300 can receive and transmit data via a two-wire serial interface.

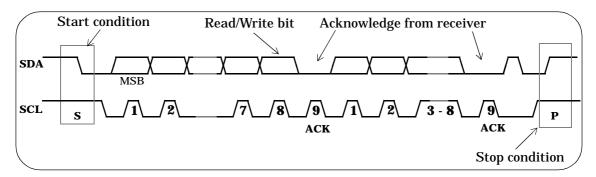

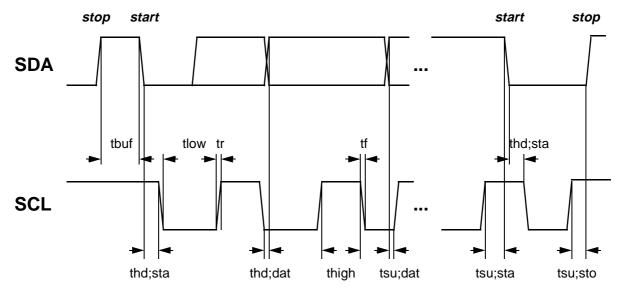

## **Serial Communication Protocol**

The host must perform the role of a communications master and the camera acts as either a slave receiver or transmitter. The communication from host to camera takes the form of 8-bit data with a maximum serial clock frequency of up to 100kHz. Since the serial clock is generated by the host it determines the data transfer rate. The bus address for VV6300 is  $20_{\rm H}$ . Data transfer protocol on the bus is shown below.

**Data Transfer Protocol**

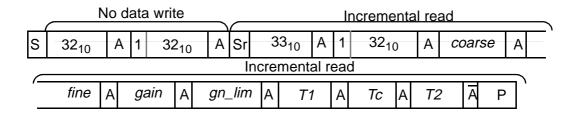

## Data format

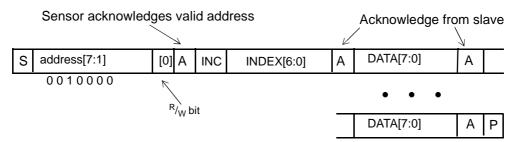

A message contains at least two bytes preceded by a *start* condition and followed by either a *stop* or *repeated start* followed by another message.

The first byte contains the device address byte which includes the data direction read/write bit. The device address is  $32_{10}$  Write,  $33_{10}$  Read. The 5 msbs of the address byte are fixed as  $0010_{-}0_{2}$ . The lsb of the address byte indicates the direction of the message. An even address causes the addressed slave to receive information from the master (write), an odd address indicates message read by the master.

#### **Data Format**

After the read/write bit is sampled, the data direction cannot be changed, until the read/write bit next message is received. The next byte contains the location of the first data byte (also referred to as the *index*). There may be up to 128 such locations. If the msb of the second byte is set the automatic increment feature of the address index is selected.

#### Message interpretation

All serial interface communications with the sensor must begin with a *start* condition. If the *start* condition is followed by a valid address byte then further communications can take place. The sensor will acknowledge the receipt of a valid address by driving SDA low. The state of the read/write bit (lsb of the address byte) is stored and the next byte of data can be interpreted.

During a write sequence the second byte received is an address index and is used to point to one of the internal registers. The msbit of the following byte is the *index auto increment* flag. If this flag is set then the serial interface will automatically increment the index address by one location after each slave acknowledge. The master can therefore send data bytes continuously to the slave until the slave fails to provide an acknowledge or the master terminates the write communication with a *stop* condition or sends a *repeated start*, *(Sr)*. If the auto increment feature is used the master does *not* have to send indexes to accompany the data bytes.

As data is received by the slave it is written bit by bit to a serial/parallel register. After each data byte has been received by the slave, an acknowledge is generated, the data is then stored in the internal register addressed by the current index.

During a read message, the current index is read out in the byte following the device address byte. The next byte read from the slave device are the contents of the register addressed by the current index. The contents of this register are then parallel loaded into the serial/parallel register and clocked out of the device by *scl*. At the end of each byte, in both read and write message sequences, an acknowledge is issued by the receiving device. Although VV6300 is always considered to be a slave device, it acts as a transmitter when the bus master requests a read from the sensor.

At the end of a sequence of incremental reads or writes, the terminal index value in the register will be one *greater* the last location read from or written to. A subsequent read will use this index to begin retrieving data from the internal registers.

A message can only be terminated by the bus master, either by issuing a stop condition, a repeated start condition or by a negative acknowledge after reading a complete byte during a read operation.

#### The programmers model

There are 128, 8-bit registers within the camera, accessible by the user via the serial interface. They are grouped according to function with each group occupying a 16-byte page of the location address space. There are eight such groups, The primary categories are given below:

- · Setup registers with bit significant functions including status (read only) bits

- Exposure parameters that influence output image brightness.

- System functions and test bit significant registers.

Any internal register that can be written to can also be read from.

|        | Index    | Name       | R/W | Default                                   | Comments                                                        |

|--------|----------|------------|-----|-------------------------------------------|-----------------------------------------------------------------|

|        | 000_0000 |            | RO  | 1100 0000 <sub>2</sub> (C0 <sub>H</sub> ) |                                                                 |

|        | 000_0001 |            | RO  | 0001 0010 <sub>2</sub> (12 <sub>H</sub> ) | Reserved                                                        |

|        | 000_0010 | status0    | RO  | 0000 1000 <sub>2</sub> (08 <sub>H</sub> ) | System status information                                       |

|        | 000_0011 | unused     | -   |                                           |                                                                 |

| sr     | 000_0100 | line_count | RO  |                                           | Current line counter value                                      |

| Status | 000_0101 | leftav     | RO  |                                           | Average value of pixels in the first half of the current line.  |

|        | 000_0110 | rghtav     | RO  |                                           | Average value of pixels in the second half of the current line. |

|        | 000_0111 | frame_av   | RO  |                                           | Average value of pixels in a frame.                             |

|        | 000_1000 | bin1       | RO  |                                           | Partial frame average - bin1                                    |

|        | 000_1001 | bin2       | RO  |                                           | Partial frame average - bin2                                    |

|        | 000_1010 | bin3       | RO  |                                           | Partial frame average - bin3                                    |

|        | 000_1011 | bin4       | RO  |                                           | Partial frame average - bin4                                    |

|        | 000_11xx | unused     | -   |                                           |                                                                 |

|        | 001_0000 | setup0     | R/W | 0010_0111 <sub>2</sub> (27 <sub>H</sub> ) | Configure the digital logic                                     |

|        | 001_0001 | setup1     | R/W | 0111_0000 <sub>2</sub> (70 <sub>H</sub> ) | Configure the digital logic                                     |

|        | 001_0010 | setup2     | R/W | 0001_1111 <sub>2</sub> (1F <sub>H</sub> ) | Pixel counter reset value                                       |

| dn     | 001_0011 | setup3     | R/W | 0000_1111 <sub>2</sub> (0F <sub>H</sub> ) | Exposure control modes                                          |

| Setup  | 001_0100 | setup4     | R/W | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | FST/QCK options                                                 |

|        | 001_0101 | unused     | -   |                                           |                                                                 |

|        | 001_011x | unused     | -   |                                           |                                                                 |

|        | 001_1xxx | unused     | -   |                                           |                                                                 |

|        | 010_0000 | unused     | -   |                                           |                                                                 |

|        | 010_0001 | fine       | R/W | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | Fine exposure initially zero                                    |

|        | 010_0010 | unused     | -   |                                           |                                                                 |

|        | 010_0011 | coarse     | R/W | 0111_0000 <sub>2</sub> (70 <sub>H</sub> ) | Coarse exposure                                                 |

| ure    | 010_0100 | gain       | R/W | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | Gain value                                                      |

| sur    | 010_0101 | clk_div    | R/W | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | Clock division                                                  |

| Exposi | 010_0110 | gn_lim     | R/W | 0000_0111 <sub>2</sub> (07 <sub>H</sub> ) | Maximum allowable gain                                          |

| ш      | 010_0111 | tl         | R/W | 0101_0101 <sub>2</sub> (55 <sub>H</sub> ) | Lower exposure control threshold.                               |

|        | 010_1000 | tc         | R/W | 1001_0110 <sub>2</sub> (64 <sub>H</sub> ) | Centre exposure control threshold.                              |

|        | 010_1001 | th         | R/W | 0110_0110 <sub>2</sub> (73 <sub>H</sub> ) | Upper exposure control threshold.                               |

|        | 010_101x | unused     | -   |                                           |                                                                 |

|        | 010_1xxx | unused     | -   |                                           |                                                                 |

|        | 111_0011 | xfav       | R/W | 1000_0000 <sub>2</sub> (80 <sub>H</sub> ) | External frame average                                          |

| _      | 111_0101 | dcth       | R/W | 1000_0000 <sub>2</sub> (80 <sub>H</sub> ) | Digital comparator threshold                                    |

| ten    | 111_1001 | unused     |     |                                           |                                                                 |

| System | 111_1010 | unused     |     |                                           |                                                                 |

| 0,     | 111_1011 | unused     |     |                                           |                                                                 |

|        | 111_11xx | unused     |     |                                           |                                                                 |

#### The programmers model

A detailed description of each register follows. The address indexes are shown as binary in brackets.

## Status 0 [000\_0010<sub>2</sub>]

The loading of certain system parameters is timed to avoid disturbing the video signal part way through a frame. Bits 0-2 can be polled to check that a value written to either the exposure, gain or clock division registers has been consumed or not. Bit 3 is essentially an internal flag differentiating between consecutive frames.

| Bit | Function                               | Default | Comment                                                                                                                                                                                                                              |

|-----|----------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Exposure value update pending          | 0       | New exposure setting sent but not yet con-<br>sumed by the exposure controller                                                                                                                                                       |

| 1   | Clock division value update<br>pending | 0       | New clock division setting sent but not yet consumed by the exposure controller                                                                                                                                                      |

| 2   | Gain value update pending              | 0       | New gain value sent but not yet consumed by the exposure controller                                                                                                                                                                  |

| 3   | Odd/even frame                         | 0       | The flag will toggle state on alternate frames                                                                                                                                                                                       |

| 4   | Black Calibration fail flag            | 0       | If the black calibration algorithm returns very<br>poor black levels - outwith both the calibration<br>and monitor windows then this flag will be set<br>and it will stay set until the next successful cal-<br>ibration is complete |

| 7:5 | Unused                                 | 0       |                                                                                                                                                                                                                                      |

## Status 0 [000\_00102]

## Line\_count [000\_0100<sub>2</sub>]

| Bits | Function   | Default                | Comment                     |

|------|------------|------------------------|-----------------------------|

| 7:0  | Line count | 0000_0000 <sub>2</sub> | Displays current line count |

## Line\_count [000\_0100<sub>2</sub>]

The video timing logic is controlled by the pixel counter and the line counter. To reduce the level of digital switching noise these counters implement a gray count sequence, where only a single counter register can change state in a clock period. However the gray count sequence is user unfriendly,e.q. 248,232,233, 235,234. A binary version of the line count is generated internally, realising a 0,1,2,3,4.... sequence, and it is this count sequence that is read by the serial interface and hence made available to the sensor user.

## Line\_avg 0 [000\_0101<sub>2</sub>] & Line\_avg 1 [000\_0110<sub>2</sub>]

The exposure controller accumulates the pixel output values. On a line by line basis the accumulation is performed in two stages. The qualified pixels in the left half of the video line are accumulated and then stored in a latch. The process is then repeated during the right half of the video line. During the interline line period (up until the latch that stores the value for the left half of the line is updated during the next line) the latches will present valid average 8-bit pixel values for both halves of the line.

| Bits | Function     | Default | Comment                                             |

|------|--------------|---------|-----------------------------------------------------|

| 7:0  | Line average | 0       | Average pixel value for first half of current line. |

## Line\_avg 0 [000\_0101<sub>2</sub>]

| Bits | Function     | Default | Comment                                              |

|------|--------------|---------|------------------------------------------------------|

| 7:0  | Line average | 0       | Average pixel value for second half of current line. |

## Line\_avg 1 [000\_0110<sub>2</sub>]

## Frame\_avg [000\_0111<sub>2</sub>]

The average pixel values stored in latches halfway through and at the end of each active video line are ultimately stored in bins that will maintain a frame sum of the pixel values. At the end of the frame the values stored in these bins are used to determine the overall pixel average for the whole frame.

| Bits | Function      | Default | Comment                          |

|------|---------------|---------|----------------------------------|

| 7:0  | Frame average | 0       | Pixel average for previous frame |

Frame\_avg [000\_0111<sub>2</sub>]

## Bin1\_avg [000\_1000<sub>2</sub>]

| Bits | Function     | Default | Comment                        |

|------|--------------|---------|--------------------------------|

| 7:0  | Bin1 average | 0       | Pixel average for current line |

Bin1\_avg [000\_1000<sub>2</sub>]

### Bin2\_avg [000\_1001<sub>2</sub>]

| Bits | Function     | Default | Comment                        |

|------|--------------|---------|--------------------------------|

| 7:0  | Bin2 average | 0       | Pixel average for current line |

#### Bin2\_avg [000\_1001<sub>2</sub>]

## Bin3\_avg [000\_1010<sub>2</sub>]

| Bits | Function     | Default | Comment                        |

|------|--------------|---------|--------------------------------|

| 7:0  | Bin3 average | 0       | Pixel average for current line |

## Bin3\_avg [000\_1010<sub>2</sub>]

#### Bin4\_avg [000\_1011<sub>2</sub>]

| Bits | Function     | Default | Comment                        |

|------|--------------|---------|--------------------------------|

| 7:0  | Bin4 average | 0       | Pixel average for current line |

## Bin4\_avg [000\_1011<sub>2</sub>]

## Setup 0 [001\_0000<sub>2</sub>]

Setup registers 0,1,2,3 and 4 are used to alter the operating parameters of the sensor. All of these registers can be written to and read from.

Setup 0 register controls some fundamental exposure and output format parameters. Defaults are shown in **Bold.**

| Bit | Function                                                       | Default | Comment                                                                                                                                                              |

|-----|----------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Automatic exposure control.<br>Off/ <b>On</b>                  | 1       | Enables or disables automatic exposure control.<br>Current exposure value is frozen when disabled.                                                                   |

| 1   | Clamp fine exposure<br>Off/ <b>On</b>                          | 1       | If this bit is set <i>and</i> aec is enabled <i>and</i> the coarse<br>exposure has exceeded the clamp threshold, 16,<br>then the fine exposure will be clamped to 0. |

| 2   | Automatic gain control.<br>Off/ <b>On</b>                      | 1       | Enables or disables automatic gain control. Current gain value is frozen when disabled.                                                                              |

| 3   | Enable immediate gain<br>update.<br><b>Off</b> /On             | 0       | Allow manual change to gain to be applied imme-<br>diately.                                                                                                          |

| 4   | Enable immediate clock divi-<br>sion update.<br><b>Off</b> /On | 0       | Allow manual change to clock division to be applied immediately.                                                                                                     |

| 6:5 | Data format select.                                            | 01      | 00 - 8 wire parallel output<br><b>01 - 4 wire parallel output</b><br>10 - 2 wire serial output<br>11 - 1 wire serial output                                          |

| 7   | 3/4 crystal clock<br><b>Off</b> /On                            | 0       | Achieves clock division by 3 rather than 4.                                                                                                                          |

## Setup0 [001\_00002]

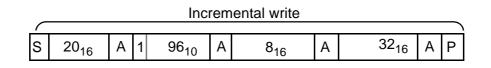

## Setup 1 [001\_0001<sub>2</sub>]

Setup 1 register controls registers that are less likely to be modified on a regular basis. The user should note that the border pixels/lines can be disabled/enabled independently from the enabling/disabling of the custom analogue horizontal shift register.

| Bit | Function                                           | Default | Comment                                                                                                                              |

|-----|----------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Enable additional black lines (3-8) <b>Off/</b> On | 0       | If enabled extra black lines are visible at device output                                                                            |

| 1   | Enable border pixels<br><b>Off</b> /On             | 0       | Extends qualified image size to 164 x 124. Default image size is 160 x 120                                                           |

| 2   | Enable horizontal shuffle mode.<br><b>Off</b> /On  | 0       | The contents of the horizontal shift register<br>are shuffled so that all the even columns then<br>all the odd columns are read out. |

Setup1 [001\_0001<sub>2</sub>]

| Bit | Function                                          | Default | Comment                                                                                                                                                                                                         |

|-----|---------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | Enable sample mode<br><b>Off</b> /On              | 0       | If enabled the data bus will continuously output a " $96_{\text{H}}$ " pattern. With the sensor in this mode a user can determine the best point at which to sample the data.                                   |

| 4   | Status line data output enable.<br>Off/ <b>On</b> | 1       | Enables the output of serial interface status<br>information on the data bus. By default the<br>bottom 64 locations from the serial interface<br>will be output.                                                |

| 5   | 8-bit or 4-bit ADC select                         | 1       | The analogue output ADC can be configured to convert to 4-bit or 8-bit resolution.                                                                                                                              |

| 6   | 50fps timing/ <b>60fps timing</b>                 | 1       | The sensor will implement 60Hz like line<br>timing by default giving reduced flicker<br>operation with 60Hz source frequencies. If the<br>supply frequency is 50Hz then 50Hz like<br>timing should be selected. |

| 7   | External frame average<br><b>Off</b> /On          | 0       | Normally the accumulator arithmetic logic calculates the frame average of the pixel samples. However if this bit is enabled then the user may specify a frame average.                                          |

Setup1 [001\_0001<sub>2</sub>]

## Setup 2 [001\_0010<sub>2</sub>]

In many systems VV6300 will be continuously synchronised. During this synchronisation the video timing is reset to a fixed point within the frame timing. The counter reset value is definable.

| Bit | Function                                            | Default             | Comment                                                                     |

|-----|-----------------------------------------------------|---------------------|-----------------------------------------------------------------------------|

| 5:0 | Pixel counter reset value.                          | 011111 <sub>2</sub> | During synchronisation the pixel counter is reset to the defined value.     |

| 6   | Status information output option.<br><b>Off</b> /On | 0                   | Selects which system parameters are output on status line. See table below. |

| 7   | Status information output option. <b>Off</b> /On    | 0                   | Selects which system parameters are output on status line. See table below. |

| Setup | 2 | [001_ | _0010 | ) <sub>2</sub> ] |

|-------|---|-------|-------|------------------|

|-------|---|-------|-------|------------------|

| Bit 7 | Bit 6 | Register Address Range<br>8-bit modes | Register Address Range<br>4-bit modes |

|-------|-------|---------------------------------------|---------------------------------------|

| 0     | 0     | 00 <sub>H</sub> - 3F <sub>H</sub>     | 00 <sub>H</sub> - 1F <sub>H</sub>     |

| 0     | 1     | 40 <sub>H</sub> - 7F <sub>H</sub>     | 20 <sub>H</sub> - 3F <sub>H</sub>     |

| 1     | 0     | -                                     | 40 <sub>H</sub> - 5F <sub>H</sub>     |

| Bit 7 | Bit 6 | Register Address Range<br>8-bit modes | Register Address Range<br>4-bit modes |

|-------|-------|---------------------------------------|---------------------------------------|

| 1     | 1     | -                                     | 60 <sub>H</sub> - 7F <sub>H</sub>     |

#### **Status line information options**

### Setup 3 [001\_0011<sub>2</sub>]

| Bit | Function                      | Default           | Comment                                                                                                                             |

|-----|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 3:0 | Exposure control mode select. | 1111 <sub>2</sub> | The average value for the frame that the exposure controller uses can be calculated in a number of different ways. See table below. |

| 4   | Autoload control              | 0                 | This bit controls the autoload feature. Note1                                                                                       |

| 6:5 | Exposure step size            | 01                | Selects exposure step size. 1/8 for fast but jerky convergence to 1/64 for slow but smooth convergence. Default 1/16.               |

| 7   | Unused                        | 0                 |                                                                                                                                     |

## Setup 3 [001\_0011<sub>2</sub>]

Note1: The state of this pin can affect the autoload function in a number of ways.

1. If the autoload bit is high continuously and the autoload pin is also high then an autoload will not take place.

2. If the autoload bit is initially high and is then forced low then an autoload will take place regardless of the state of the autoload pin.

3. If the autoload pin is initially high and is then forced low an autoload will take place regardless of the state of the autoload bit.

4. A low to high transition on either the autoload bit or the autoload pin while VV6300 is running will have no effect on the autoload function.

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function          |

|-------|-------|-------|-------|-------------------|

| 0     | 0     | 0     | 0     | bin1              |

| 0     | 0     | 0     | 1     | bin2              |

| 0     | 0     | 1     | 0     | bin3              |

| 0     | 0     | 1     | 1     | bin4              |

| 0     | 1     | 0     | 0     | (bin1 + bin2) / 2 |

| 0     | 1     | 0     | 1     | (bin3 + bin4) / 2 |

| 0     | 1     | 1     | 0     | (bin1 + bin3) / 2 |

| 0     | 1     | 1     | 1     | (bin2 + bin4) / 2 |

| 1     | 0     | 0     | 0     | (bin1 + bin4) / 2 |

| 1     | 0     | 0     | 1     | (bin2 + bin3) / 2 |

**Frame Average Options**

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function                        |

|-------|-------|-------|-------|---------------------------------|

| 1     | 0     | 1     | 0     | (bin1 + bin2 + bin3 + bin4) / 4 |

| 1     | 0     | 1     | 1     | (bin1 + bin2 + bin3 + bin4) / 4 |

Frame Average Options

| Bit 6 | Bit 5 | Step size | Comment |

|-------|-------|-----------|---------|

| 0     | 0     | 1/8       |         |

| 0     | 1     | 1/16      | Default |

| 1     | 0     | 1/32      |         |

| 1     | 1     | 1/64      |         |

#### Exposure step size options

## Setup 4 [001\_0100<sub>2</sub>]

The data output on the serial wire or the 4 wire/8 wire busses can be qualified, if required, by an internally generated clock signal, QCK. This clock can be configured variously. Both a *fast* and a *slow* QCK can be generated. If the former is selected then the falling edge of the clock will qualify the current data nibble/byte, i.e. if the sensor is operating in 4 bit-4 wire mode then any true 8 bit data (e.g. line type code) will be qualified on a nibble basis. If the *slow* QCK option is preferred then both edges of this clock are used to qualify the current data nibble/byte.

The QCK function has a dedicated pin assigned, however by selecting the appropriate bits the FST pin can also output QCK data. By default QCK is disabled. However by writing the appropriate message, QCK can be forced to free run, qualify the embedded coding sequences and the visible data or the visible data only. FST can also be enabled or disabled or alternatively the FST pin can output a timing signal to synchronise several VV6300 sensors or finally the FST pin can output the state of the custom analogue block successive approximation ADC output comparator.

| Bit | Function          | Default |                                                                          | Mode                                                                              |                                                                              |

|-----|-------------------|---------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1:0 | FST/QCK pin mode. | 002     |                                                                          | FST pin                                                                           | QCK pin                                                                      |

|     |                   |         | 00 <sub>2</sub><br>01 <sub>2</sub><br>10 <sub>2</sub><br>11 <sub>2</sub> | Normal FST<br>Normal FST<br>QCK <sub>F</sub><br>Inverted QCK <sub>F</sub>         | QCK <sub>S</sub><br>QCK <sub>F</sub><br>QCK <sub>S</sub><br>QCK <sub>F</sub> |

| 3:2 | QCK mode select   | 002     | 00 <sub>2</sub><br>01 <sub>2</sub><br>10 <sub>2</sub><br>11 <sub>2</sub> | disable<br>free running<br>validate control and image<br>validate image data only |                                                                              |

| 5:4 | unused            | 002     |                                                                          |                                                                                   |                                                                              |

| 7:6 | FST mode select   | 002     | 00 <sub>2</sub><br>01 <sub>2</sub><br>10 <sub>2</sub><br>11 <sub>2</sub> | disable FST<br>enable FST<br>synchronisation pulse ou<br>output ADC comparator    |                                                                              |

Setup 4 [001\_0100<sub>2</sub>]

## Exposure Control Registers [010\_0001<sub>2</sub>] - [010\_1001<sub>2</sub>]

There is a set of parameters that control the time that the sensor pixels are exposed. The parameters are as follows: fine and coarse exposure time, clock division control and finally gain control. The latter parameter does not affect the integration period rather it amplifies the video signal at the output stage of the sensor core. An internal automatic algorithm will, if enabled, continually monitor the pixel output and then, if required, use this data to correct the current exposure.

Manually changing the divisor applied to the incoming crystal clock can alter the effective integration of the sensor. By slowing the internal clock down the integration period can be increased, i.e. halving the pixel clock frequency will double the integration period.

If the user wishes to use the automatic exposure algorithm, the automatic exposure control (controlling *fine* and *coarse* exposure) must be enabled. Additional gain control is optional. It is also possible to change the gain manually via the serial interface even if the exposure is adjusted automatically.

If a user wishes to write an external value to one of the automatic exposure algorithm registers then it is advised that the automatic control for that register be disabled prior to using the serial interface to write the external value.

*Note:* The external exposure (coarse, fine or gain) values do not take effect immediately. Data from the serial interface is read by the exposure algorithm at the start of a video frame. If the user reads an exposure value via the serial interface then the value reported will be the data as yet unconsumed by the exposure algorithm, because the serial interface logic locally stores all the data written to the sensor.

Between writing the exposure data and the point at which the data is consumed by the exposure algorithm, bit 0 of the status register is set. The gain value is updated a frame later than the coarse and fine exposure parameters. The gain is applied directly at the video output stage and does not require the long set up time of the coarse and fine exposure settings.

The automatic exposure algorithm uses a set of exposure threshold settings. These thresholds may also be modified by the user to alter the algorithm's performance. The exposure algorithm uses these thresholds in a histogram. The three thresholds divide the histogram into 4 regions, very overexposed, overexposed, underexposed and very underexposed. The pixel data received from the sensor core is compared against the thresholds to determine the accuracy of the current exposure setting. A series of flags are set to describe the outcome of the histogram comparison and the new exposure setting can then be derived.

Each exposure parameter is subject to a maximum setting. The fine exposure setting can be clamped to a fixed value regardless of the decision made by the automatic algorithm. The clamping will occur if the coarse exposure setting exceeds a predetermined value and the clamping has been enabled via the serial interface.

| Bit | Function            | Default                                   | Comment                                                                                  |

|-----|---------------------|-------------------------------------------|------------------------------------------------------------------------------------------|

| 7:0 | Fine exposure value | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | maximum fine (50Hz mode) = FF <sub>H</sub><br>maximum fine (60Hz mode) = A8 <sub>H</sub> |

## Fine Exposure Value [010\_0001<sub>2</sub>]

| Bit | Function              | Default                                   | Comment                                                 |

|-----|-----------------------|-------------------------------------------|---------------------------------------------------------|

| 7:0 | Coarse exposure value | 0111_0000 <sub>2</sub> (70 <sub>H</sub> ) | maximum coarse (50Hz and 60Hz modes)<br>91 <sub>H</sub> |

## Coarse Exposure Value [010\_0011<sub>2</sub>]

| Bit | Function   | Default | Comment                                                        |

|-----|------------|---------|----------------------------------------------------------------|

| 2:0 | Gain value | 0       | 8 possible gain states can be written via the serial interface |

## Gain Value [010\_0100<sub>2</sub>]

All 8 binary codes can be written to the core via the serial interface. Only the 4 thermometer codes 000,001,011 and 111 are selected by the automatic exposure algorithm. The 4 other codes are however still valid and will be evaluated as detailed in the table below. It is clear, from the non-linear relationship between the binary code and the actual gain applied at the analogue output stage, that care should be taken when using non thermometer code gain settings. If the user writes a gain code of 110 (real gain = 1.600) and then enables automatic gain control and the controller then decided to reduce the gain, the new gain value would be 011 (real gain = 4.000) i.e. the effective applied gain at the analogue output stage has actually been increased.

| Gain binary code | Actual signal gain |

|------------------|--------------------|

| 000              | 1.000              |

| 001              | 2.000              |

| 010              | 1.333              |

| 011              | 4.000              |

| 100              | 1.143              |

| 101              | 2.667              |

| 110              | 1.600              |

| 111              | 8.000              |

#### System Gain

| Bit | Function            | Default | Comment                                       |

|-----|---------------------|---------|-----------------------------------------------|

| 1:0 | Clock divisor value | 0       | Pixel clock = Crystal clock ÷2 <sup>n+1</sup> |

## Clock Divisor Value [010\_0101<sub>2</sub>]

The *undivided* input crystal clock is used by the clock generator circuitry, elements of the serial interface and a small number of other registers in the design. The remaining digital logic and the analogue circuitry, use internally generated clocks, namely the pixel clock and the faster ADC clocks. These clocks are all slower versions of the crystal clock. The ADC clocks may be up to half the crystal frequency, but can be further divided by factors of 2, 4 or 8. The pixel clock is in turn slower than the ADC clock. If the ADC is operating in 4 bit mode then the pixel clock is 1/4 the frequency of the ADC clock, otherwise the pixel clock will be 1/8 the frequency of the ADC clock.

| Bit | Function   | Default | Comment |

|-----|------------|---------|---------|

| 2:0 | Gain limit | 7       |         |

## Gain Limit[010\_0110<sub>2</sub>]

| Bit | Function                 | Default | Comment |

|-----|--------------------------|---------|---------|

| 7:0 | Exposure lower threshold | 85      |         |

#### Exposure Lower Threshold [010\_0111<sub>2</sub>]

| Bit | Function                  | Default | Comment |

|-----|---------------------------|---------|---------|

| 7:0 | Exposure centre threshold | 100     |         |

Exposure Centre Threshold [010\_1000<sub>2</sub>]

| Bit | Function                  | Default | Comment |

|-----|---------------------------|---------|---------|

| 7:0 | Exposure higher threshold | 115     |         |

#### Exposure Higher Threshold [010\_1001<sub>2</sub>]

## Frame Average [111\_0011<sub>2</sub>]

The exposure controller normally compiles a frame average from the data received from the core. A complete frame period is required to produce a frame average. This is clearly unacceptable for simulation and test purposes. It is possible to manually force a frame average via the serial interface. This feature together with the ability to curtail the frame duration will allow the behaviour of the exposure controller to be examined in a realistic simulation period.

This register is read/write compatible

| Bit | Function      | Default | Comment                                                                              |

|-----|---------------|---------|--------------------------------------------------------------------------------------|

| 7:0 | Frame average | 0       | Allow a synthetic frame average to be written to and used by the exposure controller |

## Digital Comparator Threshold [111\_0101<sub>2</sub>]