# Mono and Colour QSIF Digital Video CMOS Image Sensors

PRELIMINARY RELEASE

The VV5301 and VV6301 are highly integrated digital output imaging devices based on STMicroelectronics's unique CMOS sensor technology. Both of these sensors require minimal support circuitry and provide an ideal low cost imaging solution.

VV5301 (monochrome) and VV6301 (colourised) produce digital video output. The video streams from both devices contain embedded control data that can be used to enable frame grabbing applications.

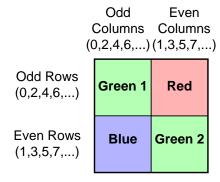

The pixel array of the VV6301 has colour filters forming a Bayer colour pattern. This sensor requires software to perform colour processing to allow an image to be displayed on a PC.

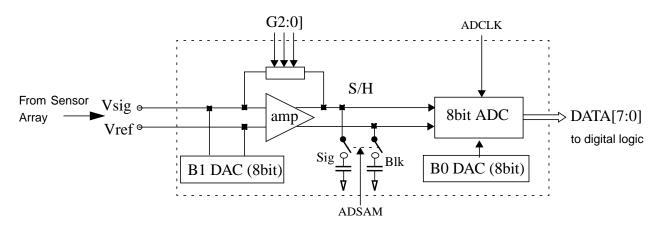

The sensor can perform automatic black calibration to remove voltage offsets in the video signal path that lead to offsets in the output image. These offsets are removed using 2 Digital to Analogue Convertors (DACs). The automatic black calibration algorithm monitors the average level of the sensor black pixels and adjusts the input level to the 2 DACs to remove the offset.

A 2 wire serial interface allows the sensor to be reconfigured if required.

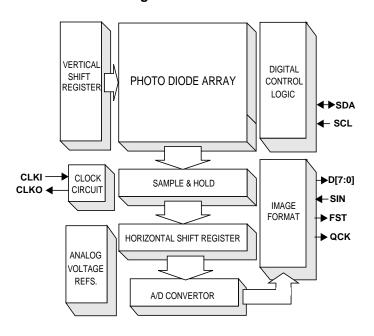

# Functional block diagram

#### **Key Features**

- · QSIF resolution sensor

- · Automatic exposure/gain control

- Multiple digital output formats available

- I2C interface for sensor control

- Integrated 8bit ADC

- On board voltage regulator

- · Automatic Black Calibration

- Variable frame rate

- · Reduced flicker operating modes

# **Application Areas**

- Toys

- Automotive systems

- Intelligent Imaging sensors

## **Specifications**

| Maximum pixel resolution                           | 164 x 124                                                                              |

|----------------------------------------------------|----------------------------------------------------------------------------------------|

| Effective image<br>size after colour<br>processing | 160 x 120                                                                              |

| Pixel size                                         | 12.0μm x 12.0μm                                                                        |

| Array size                                         | 1.92mm x 1.44mm                                                                        |

| Exposure control                                   | Automatic (range 25000:1)                                                              |

| Analogue gain                                      | +18dB                                                                                  |

| Signal/Noise ratio                                 | 36dB                                                                                   |

| Supply voltage                                     | 5V DC +/- 5%                                                                           |

| Supply current<br>VV5301-VV6301                    | 2.9mA (standby)<br>14.6mA (active)                                                     |

| Operating<br>temperature<br>(ambient)              | 0°C - 40°C<br>(for extended temperature information please contact STMicroelectronics) |

| Package type                                       | 48BGA                                                                                  |

| Table of Content |

|------------------|

|------------------|

| 1.  | Introduction                                        | 4  |

|-----|-----------------------------------------------------|----|

| 1.1 | Overview                                            | 4  |

| 1.2 | Exposure, Clock Division and Gain Control           | 4  |

| 1.3 | Digital Interface                                   | 4  |

| 2.  | Operating Modes                                     | 6  |

| 2.1 | Video Timing                                        | 6  |

| 2.2 | Pixel Array                                         | 6  |

| 2.3 | System Clock Generation                             | 9  |

| 2.4 | Calculating Sensor Framerate                        | 9  |

| 3.  | Auto Black Calibration                              | 11 |

| 4.  | Exposure Control                                    | 12 |

| 3.  | Auto Black Calibration                              | 11 |

| 4.  | Exposure Control                                    | 12 |

| 4.1 | Calculating Exposure Period                         | 12 |

| 4.2 | Automatic Exposure Control                          | 12 |

| 4.3 | Updating Exposure, Gain and Clock Division Settings | 12 |

| 4.4 | Clock Control                                       | 12 |

| 4.5 | Gain Setting                                        | 13 |

| 5.  | Timed Serial Interface Parameters                   | 14 |

| 5.1 | Listing and Categorizing the Parameters             | 14 |

| 5.2 | Timed Parameter Update Points                       | 14 |

| 6.  | Digital Video Interface Format                      | 15 |

| 6.1 | Embedded control data                               | 15 |

| 6.2 | 8-Wire Parallel Mode                                | 17 |

| 6.3 | 4-Wire Parallel Mode                                | 17 |

| 6.4 | Video Frame Composition                             | 18 |

| 6.5 | Qualifying the Output Data                          | 22 |

| 7.  | Serial Control Bus                                  | 26 |

| 7.1 | General Description                                 | 26 |

| 7.2 | Serial Communication Protocol                       | 26 |

| 7.3 | Data Format                                         | 26 |

| 7.4 | Message Interpretation                              | 27 |

| 7.5 | The Programmers Model                               | 28 |

| 7.6 | Types of messages                                   | 38 |

| 7.7 | Serial Interface Timing                             |    |

| 8.  | Detailed AC/DC Specification                        | 42 |

| 8.1 | VV5301/VV6301 AC/DC Specification                 | 42 |

|-----|---------------------------------------------------|----|

| 8.2 | VV5301/VV6301 Power Consumption                   | 42 |

| 8.3 | Digital Input Pad Pull-up and Pull-down Resistors | 42 |

| 9.  | Pinout and Pin Descriptions                       | 43 |

|     | W/5004 W/0004 Baranasa dad Bafaranas Baranas      | 4- |

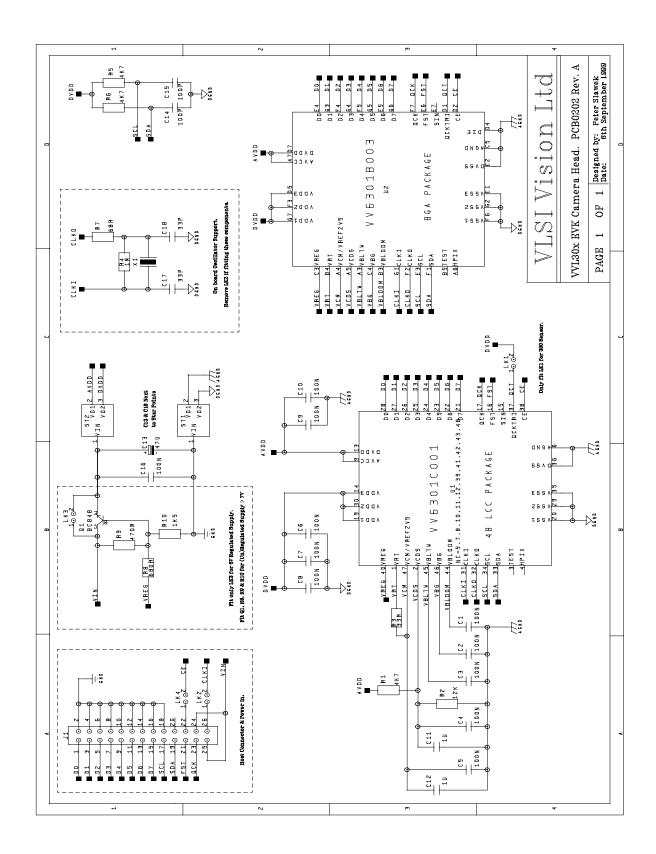

| 10. | VV5301/VV6301 Recommended Reference Design        | 45 |

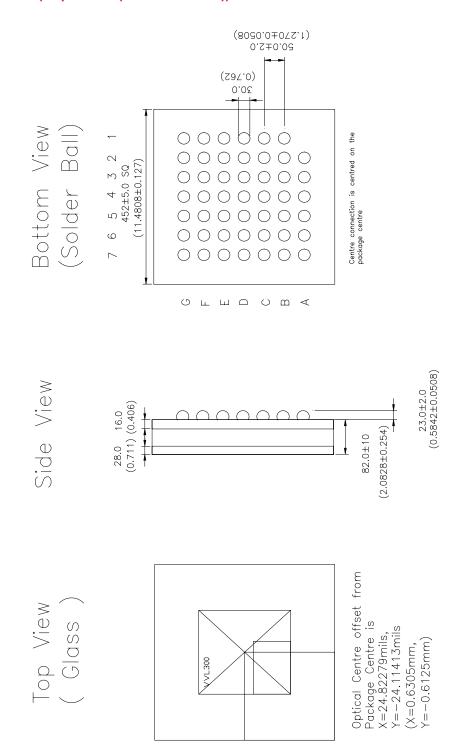

|     | Package Details (48 pin BGA (VV5301/VV6301))      |    |

| 11. | -                                                 | 46 |

#### 1. Introduction

#### 1.1 Overview

VV5301/VV6301 is a SIF format CMOS image sensor. The VV5301 sensor is a monochrome device and the VV6301 is the colourised variant.

**Important:** The sensors' output video data stream only contains raw data. A microprocessor and supporting software are required to generate a video waveform that can be displayed on a VDU

| Mode          | Input Clock<br>(MHz) <sub>Note</sub> | System<br>Clock<br>Divisor | Image Size | Line Time<br>(μs) | Lines<br>per<br>Frame | Frame Rate<br>(fps) |

|---------------|--------------------------------------|----------------------------|------------|-------------------|-----------------------|---------------------|

| QSIF - 25 fps | 14.318                               | 1                          | 164 x 124  | 271.502           | 147                   | 25.06               |

| QCIF - 30 fps | 17.73                                | 1                          | 164 x 124  | 227.36            | 147                   | 29.92               |

VV5301/VV6301 have an on-board 8bit ADC, this limits the number of components required to form a complete digital imaging system.

The VV5301/VV6301 sensor will output an image size of 164 x 124. This is an oversized QSIF image. The extra pixels that the form the 2 pixel deep border that surrounds the true QSIF image are made available to the external colour processing algorithm.

# 1.2 Exposure, Clock Division and Gain Control

VV5301/VV6301 have an internal automatic exposure/gain control algorithm. This algorithm can be disabled allowing the user to externally control the exposure. The externally calculated exposure, clock division and gain control settings would then be written to the sensor via the I2C interface.

## 1.3 Digital Interface

VV5301/VV6301 have a flexible digital interface, the main components of which are listed below:

- 1. A tri-stateable 8-wire data bus (D[7:0]) for sending both video data and embedded timing references.

- 2. 4-wire and 8-wire data bus alternatives available.

- 3. A data qualification clock, QCK, which can be programmable via the serial interface to behave in a number of different ways (Tri-stateable).

- 4. A line start signal, LST (Tri-stateable).

- 5. A frame start signal, FST (Tri-stateable).

- 6. OEB tri-states all 5 data bus lines, D[4:0], the qualification clock, QCK and FST.

- 7. The ability to synchronise the operation of multiple cameras (sensor produces a synchronisation out pulse, SNO).

- 8. A 2-wire serial interface (SDA,SCL) for controlling and setting up the device.

# 1.3.1 Digital Data Bus

Along with the pixel data, codes representing the start and end of fields and the start and end of lines are embedded within the video data stream to allow a co-processor to synchronise with video data the camera module is generating Section 6.defines the format for the output video data stream.

## 1.3.2 Frame Grabber Control Signals

To complement the embedded control sequences the data qualification clock (QCK) and the field start signal (FST) signals can be independently set-up as follows:

- 1. Disabled

- 2. Free-running.

- 3. Qualify only the control sequences and the pixel data.

- 4. Qualify the pixel data only

477

#### 1.3.3 2-wire Serial Interface

The 2-wire serial interface provides complete control over sensor setup and operation. Two serial interface broadcast addresses are supported. One allows all sensors to be written to in parallel while the other allows all sensors and co-processors to be written to in parallel.

Section 7. defines the serial interface communications protocol and the register map of all the locations which can be accessed via the serial interface.

### 1.4 Other Features

# 1.4.1 Tristating Digital Outputs

The QCK, FST and Databus[7:0] pins can be tristated. The QCK pin can be independently tristated by driving the QCKTRI pin low. The QCK, FST and upper nibble of the Databus can also be tristated via a serial register control bit, see register[116] for more details. The lower nibble of the Databus can also be independently tristated using a different control bit in register[116].

## 1.4.2 Synchronising Video Timing

The video timing logic in VV5301/VV6301 can be synchronised, i.e. reset to the beginning of a timing field, by an external pin, SIN. This pin is normally low. To enable the synchronising feature the user must drive the pin high for a number of clock periods, c.10 CLKI periods, then drive it low again. This synchronisation should only be done every other field as the sensor has a 2 field repeat cycle requirement for the video timing. If the SIN pin was asserted every field the exposure controller and application of new external exposure and gain settings would not operate correctly.

#### 1.4.3 Pixel Hold Feature

The HPIX signal can be used to freeze the internal ADC, forcing the sensor to stop converting new pixel values. If the HPIX is driven high then the ADC will maintain the currently converted pixel value. This feature is intended to function as an external pixel defect correction system, albeit a ver basic example.

VV5301 & VV6301 **Operating Modes**

#### 2. **Operating Modes**

#### 2.1 Video Timing

The video format mode on power-up is QSIF 30fps by default, although a 25fps mode can also be selected, see serial register[17], bit 6. The number of active video lines in each mode is the same (124) for both the QSIF modes. The slower frame rate (25 fps) is implemented by simply extending the line period from 203 pixel periods to 301 pixel periods.

Table 1 details the setup for each of the video timing modes.

| Video<br>Mode | Clock<br>(MHz) | System Clock Divisor | Video Data | Line Length | Field<br>Length | Output<br>Mode |

|---------------|----------------|----------------------|------------|-------------|-----------------|----------------|

| QSIF (30fps)  | 14.318         | 1                    | 164 x 124  | 203         | 147             | 4-wire         |

| QSIF (25fps)  | 17.73          | 1                    | 164 x 124  | 301         | 147             | 4-wire         |

**Table 1: Video Timing Modes**

#### 2.2 **Pixel Array**

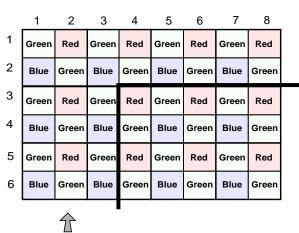

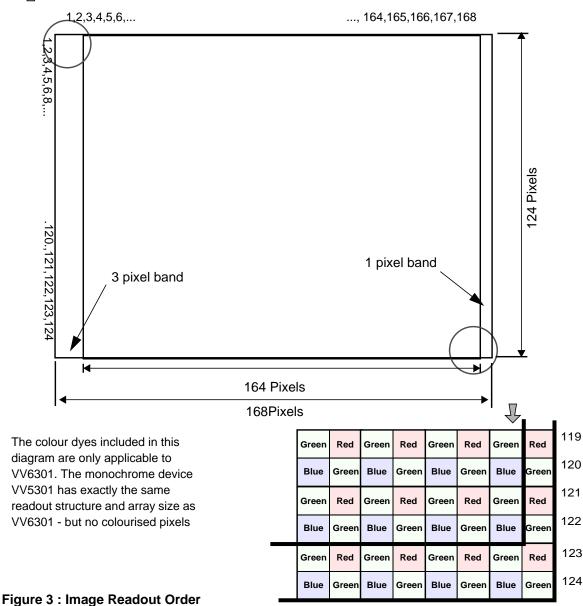

The physical pixel array is 168 x 124 pixels. The pixel size is 12.0 μm by 12.0 μm. The output video image size is 164 x 124 pixels. The border pixels from the array are used as a shield from edge effects.

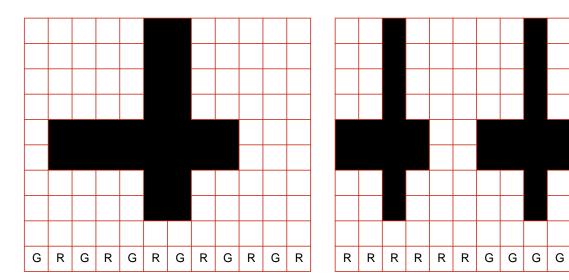

Figure 3 shows how the 164 x 124 is aligned within the bigger 168 x 124 pixel array. Image read-out is flexible. By default the sensor read out is configured to be horizontally 'non-shuffled' non-interlaced raster scan. The horizontally 'shuffled' raster scan order differs from a conventional raster in that the pixels of individual rows are re-ordered, with the even pixels within a row readout first, followed by the odd pixels. This 'shuffled' read-out within a line, groups pixels of the same colour (according to the Bayer pattern - Figure 1) together, reducing cross talk between the colour channels. The horizontal shuffle option would normally only be selected with the colour sensor variant, VV6301.

Figure 1 : Bayer Colourisation Pattern (VV6301 only)

VV5301 & VV6301

G

G

Where G - Green and R - Red

Figure 2 : Horizontal Shuffle Enabled

Please note the column read out order. If the readout is unshuffled then the readout order is even,odd,even etc. If the readout is shuffled, to avoid colour channel crosstalk, then all the even columns are readout first followed by the odd columns.

161

162

163

164

165

166

168

167

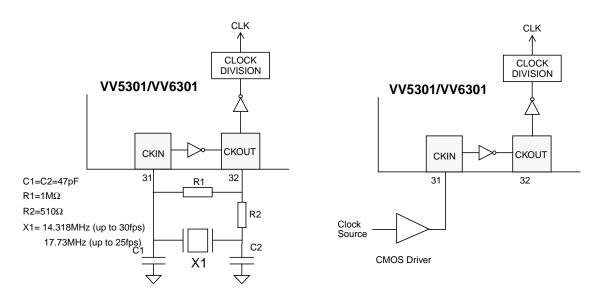

### 2.3 System Clock Generation

VV5301/VV6301 generates a system clock when a quartz crystal or ceramic resonator circuit is connected to the CLKI and CLKO pins. The device can also be driven directly from an external clock source driving CLKI.

Figure 4: Camera Clock Source

For greater flexibility the input frequency can be divided by 1, 2, 4 or 8 to select the pixel clock frequency. Two bits in the clock division register in the serial interface select the input clock frequency divisor. The table below gives the different frame rates that can be selected, when CLKI = 14.318MHz, for up to 30frames per second, for each divisor.

| CLKI (MHz) | Divisor | Pixel Period (us) | Frame Rate | Comments |

|------------|---------|-------------------|------------|----------|

| 14.318     | 1       | 1.1175            | 29.99      | default  |

| 14.318     | 2       | 2.235             | 15.01      |          |

| 14.318     | 4       | 4.47              | 7.5        |          |

| 14.318     | 8       | 8.94              | 3.75       |          |

Table 2: Clock Division (60Hz Video Mode)

## 2.4 Calculating Sensor Framerate

The VV5301/VV6301 frame rate depends upon:

- the frequency of the system clock (CLKI)

- the ADC conversion accuracy (8-bit)

- the internal clock divisor selected (1, 2, 4, or 8)

- the output format is a constant 2

User can set their own values for CLKI and also the clock divisor setting. The frame rate is determined as follows

An example is given with a clock input of 14.318MHz, 160 x120 (164 x 124) image format, 8-bit ADC conversion rate and a clock divisor of 2.

- 1. Determine clock input (CLKI) frequency 14.318MHz

- 2. Pixel period = (divisor x conversion factor x output format factor) / CLKI

47/

cd5301\_6301\_f.fm

9/49

VV5301 & VV6301 Operating Modes

Clock divisor = 1, 2, 4 or 8.

Conversion factor = 8 for 8-bit ADC accuracy

Output format factor is 2

Example: Pixel period =  $(2 \times 8 \times 2) / 14.318$ MHz = **2.235** $\mu$ s

3. Line period = (no. of visible pixels + line overhead) x pixel period

The number of visible pixels per line is 160. The interline pixel period overhead (including the 4 border pixels that can be enabled to qualify extra video information) is mode dependent, 43 pixel periods for 60Hz mode or 141 pixel periods for 50Hz mode.

Example: Line period =  $(160 + 43) \times 2.235 \mu s = 453.705 \mu s$

**4.** Frame period = (no. of visible lines + frame overhead) x line period

For the purposes of calculating the effective frame rate the number of active lines is assumed to be fixed at 120. The frame overhead (which includes the 4 border lines that can be enabled to qualify extra video information) has a constant value of 27 line periods.

Example: Frame period =  $(120 + 27) \times 453.705 \mu s = 66.694 ms$

giving a frame rate = 1 / frame period = 15 frames per second

VV5301 & VV6301

#### 3. Auto Black Calibration

Black calibration is used to remove voltage offsets that cause shifts in the black level of the video signal. The VV5/6301 is equipped with an automatic function that continually monitors the output black level and calibrates if it has moved out of range. The signal is corrected using two "Black-Cal" DACs, B0 and B1, shown below

Figure 5: Block Diagram of Black Calibration System

Black calibration can be split into two stages, **monitor** (1 cycle over 2 lines) and **update** (3 cycles, each cycle takes 2 lines). During the monitor phase the current black level is compared against two threshold values. If the current value falls outside the threshold window then an update cycle is triggered. The update cycle can also be triggered by a change in the gain applied to sensor core or via the serial interface.

#### 3.1 Monitor Procedure

The decision on when to re-calibrate the black level is made during the first cycle through the black reference lines. The decision area for the black monitor is by default the last 16 pixels of the middle 128 pixels of the second designated black line, line 2. However if this set of pixels fail to give a "good" black level then it is possible to use the penultimate group of 16 pixels.

The black reference pixels are summed, averaged and then compared with the monitor window. If the average falls outside the window a flag is then set to force a re-calibration of the DAC values.

#### 3.2 Update

The black calibration update sequence requires three phases and is performed over the remaining black lines at the start of the video field, lines 3 to 8. During the first phase initial B0 DAC calibration is performed. In the second, the B1 DAC is calibrated within the limitation of its step size. In the final phase the black level is fine tuned by re-calibrating the B0 DAC. This is due to the B1 DAC having a relatively coarse step size when high gain is applied.

The two calibration phases for the B0 DAC differ in that the first time it is calibrated it is working on common mode data. During the final phase the B0 DAC is fine-tuned using black reference pixels.

**Exposure Control**

#### **Exposure Control**

#### 4.1 **Calculating Exposure Period**

The exposure time, comprising coarse and fine components, for a pixel and the analogue gain are programmable via the serial interface.

The coarse exposure value sets the number of complete lines a pixel exposes for, while the fine exposure sets the number of additional pixel clock cycles a pixel integrates for. The sum of the two gives the overall exposure time for the pixel array.

Exposure Time = ((Coarse setting x Line Period) + (Fine setting)) x (CLKI clock period) x Clock Divider Rationate1

note1: Clock Divider Ratio = 1/(Basic Clock Division \* Optional Pixel Clock Divisor)

#### 4.2 **Automatic Exposure Control**

With automatic exposure control selected VV5301/VV6301 uses a complex algorithm to automatically set the exposure value for the current scene. When combined with clock control and gain control the VV5301/VV6301 can operate over a very wide range of illumination levels.

#### 4.3 **Updating Exposure, Gain and Clock Division Settings**

Although the user can write a new exposure, gain or clock division parameter at any point within the field the sensor will only consume these new external values at a certain point. The exception to this behaviour are when the user has selected immediate update of gain If the user has selected the former then the new gain value will be applied as soon as the serial interface message has completed. The fine and coarse exposure values are always written in a "timed" manner. There are two "update pending" flags available to the user (see Status0 reg[2] for details) that allows the user to detect when the sensor has consumed one of the timed parameters. In the next section of this document we will detail all the timed parameters and describe when they are updated.

It is important to realise that there is a 1 frame latency between a new exposure value being applied to the sensor array and the results of this new exposure value being read-out. The same latency does not exist for the gain value. To ensure that the effect of the new exposure and gain values are coincident the sensor delays the application of the new gain value by approximately one frame relative to the application of the new exposure value.

If the user is using the autoincrement option in the serial interface when writing a new series of exposure/gain and clock division parameters then it is important to ensure that the sensor receives the complete message bunch before updating any of the parameters. It is also important that the timed parameters are updated in the correct order, we will discuss this fully in the next section. If an autoincrement message sequence is in progress but we have reached the point in the field timing where the gain value would normally be updated, we actually inhibit the update. We inhibit the update to ensure that the gain change is not passed to the sensor while a change in the exposure is still pending.

#### 4.4 **Clock Control**

The system clock can be divided down internally to extend the operating range of VV5301/VV6301 by allowing longer exposure times. The clock divisor options are as follows:

| Clock divisor register | Effective clock division |

|------------------------|--------------------------|

| 2'b00                  | 1                        |

| 2'b01                  | 2                        |

| 2'b10                  | 4                        |

| 2'b11                  | 8                        |

Table 3: Available clock division

If the user increases the clock divisor setting then the effective exposure period is also increased.

VV5301 & VV6301

#### 4.5 **Gain Setting**

An external gain value can be written to the sensor as follows.

| Gain binary code | Effective system gain |

|------------------|-----------------------|

| 000              | 1.000                 |

| 001              | 2.000                 |

| 010              | 1.333                 |

| 011              | 4.000                 |

| 100              | 1.143                 |

| 101              | 2.667                 |

| 110              | 1.600                 |

| 111              | 8.000                 |

Table 4: Gain settings

If the image is to dark and the exposure is already close to its maximum the automatic exposure algorithm will attempt to use extra steps of gain to improve the image brightness. Each change applied by the internal algorithm will double the current value. To compensate for this increase in gain the current exposure is set to half of the maximum value. This should ensure that the user will not be aware of a step change in the scene brightness.

Similarly if the image is too bright and the integration period is short then gain will be reduced by one step (i.e. divide by two). As before, the exposure value is set to half the maximum integration period. The exposure controller can then adjust the exposure value as necessary to provide a correctly exposed image.

If the user disables the automatic exposure/gain controller then the extra gain settings detailed in Table 4 above are available.

## 5. Timed Serial Interface Parameters

The previous section, Exposure Control, introduced the concept of a "timed parameter", that is information that is written via the serial interface but will not be used immediately by the sensor, rather there will be a delay before the information is passed to the internal registers (referred to as the working registers) from the serial interface registers (referred to as the shadow registers). It is the contents of the working registers that will determine sensor behaviour.

## 5.1 Listing and Categorizing the Parameters

The timed parameters are split into 2 categories as follows:

- · fine and coarse exposure

- gain

There is a "pending" flag for each of the above categories. These flags are stored in Status0 Register[2] in bits [0] and [2]. If one of the flags is high this indicates that the working register/s controlled by that flag have yet to be updated from the according shadow register/s. This feedback information could be useful if a user is, for example, attempting to write an external exposure controller. The status of the pending flags allows accurate timing of the serial interface communications.

## 5.1.1 Fine and Coarse Exposure

The exposure category comprises registers[32,33] and [34,35].

### 5.1.2 Gain

The gain category simply comprises register[36].

## 5.2 Timed Parameter Update Points

The timed parameter categories are updated as follows:

note: We refer to odd and even fields in the table below. Each field is identical in length but we have to be able to differentiate between fields to enable correct updating of register parameters.

| Timed parameter category | Updated point                                                                                            |  |

|--------------------------|----------------------------------------------------------------------------------------------------------|--|

| fine and coarse exposure | During the interline period between the last line of the odd field and the first line of the even field. |  |

| gain                     | During the interline period between line 143 and line 144 in the even field.                             |  |

**Table 5: Timed Parameter Update Points**

If a change in exposure and gain are pending at the same time then the exposure value will be updated first followed by the gain. This will ensure image illumination continuity from field to field.

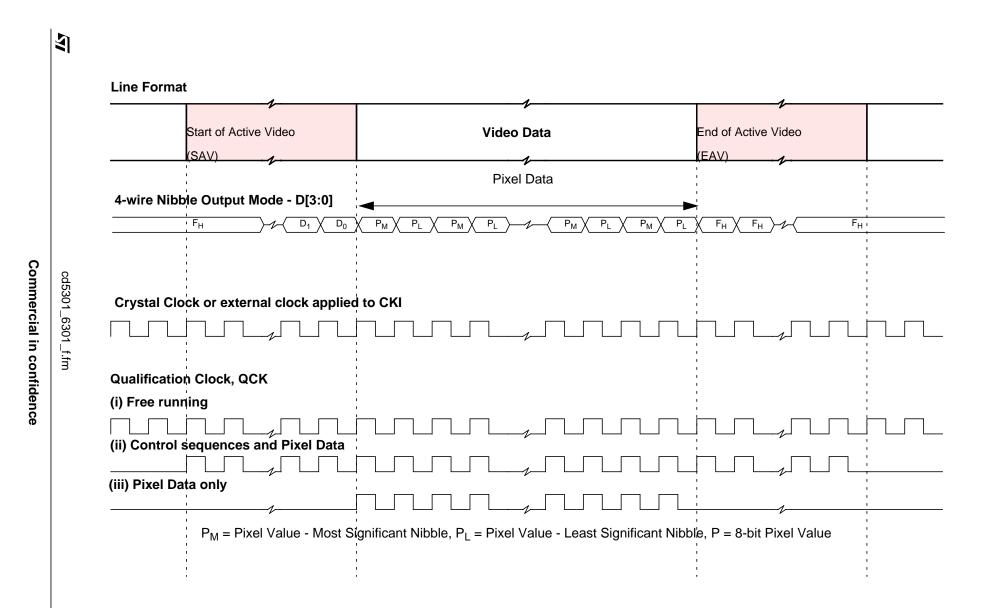

## 6. Digital Video Interface Format

The video interface consists of a bidirectional, tri-stateable 5-wire data bus. The nibble transmission is synchronised to the rising edge of the system clock.

| Read-out Order                                                      | Progressive Scan (Non-interlaced)                                                                                                                                                               |    |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Form of encoding                                                    | Uniformly quantised, PCM, 8/10 bits per sample                                                                                                                                                  |    |  |

| Correspondence between video signal levels and quantisation levels: | The internal 10-bit pixel data is clipped to ensure that $0_{\rm H}$ and $3{\rm FF_H}$ (5 Wire) or ${\rm FF_H}$ (4/8 Wire) values do not occur when pixel data is being output on the data bus. |    |  |

|                                                                     | VV5301/VV6301                                                                                                                                                                                   |    |  |

|                                                                     | 8-Bit Data                                                                                                                                                                                      |    |  |

|                                                                     | Pixel Values 1 to 254                                                                                                                                                                           |    |  |

|                                                                     | Black Level                                                                                                                                                                                     | 16 |  |

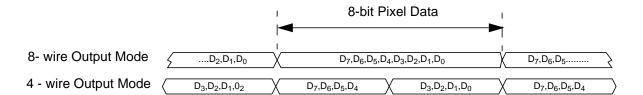

Digital video data is 8 bits per sample in VV5301 and VV6301. The data can be transmitted in the following ways:

- A single 8 bit byte over 8 output wires<sub>note</sub>.

- · A series pair of 4-bit nibbles, most significant nibble first, on 4 wires.

Figure 6: Output Modes

## 6.1 Embedded control data

To distinguish the control data from the sampled video data all control data is encapsulated in embedded control sequences. These are 6 bytes long and include a combined escape/sync character sequence, 1 control byte (the 'command byte') and 2 bytes of supplementary data.

To minimise the susceptibility of the embedded control data to random bit errors redundant coding techniques have been used to allow single bit errors in the embedded control words to be corrected. However, more serious corruption of control words or the corruption of escape/sync characters cannot be tolerated without loss of sync to the data stream. To ensure that a loss of sync is detected a simple set of rules has been devised. The four exceptions to the rules are outlined below:

- 1. Data containing a command word that has two bit errors.

- 2. Data containing two 'end of line' codes that are not separated by a 'start of line' code.

- 3. Data preceding an 'end of field' code before a start of frame' code has been received.

- 4. Data containing line that do not have sequential line numbers (excluding the 'end of field' line).

If the receiving software or hardware detects one of these violations then it should abandon the current field of video

## 6.1.1 The combined escape and sync character

Each embedded control sequence begins with a combined escape and sync character that is made up of three words. The first two of these are  $FF_H$   $FF_{H^-}$  constituting two words that are illegal in normal data. The next word is  $00_H$  - guaranteeing a clear

cd5301\_6301\_f.fm 15/49

signal transition that allows a video processor to determine the position of the word boundaries in the serial stream of nibbles. Combined escape and sync characters are always followed by a command byte - making up the four byte minimum embedded control sequence.

### 6.1.2 The command word

The byte that follows the combined escape/sync characters defines the type of embedded control data. Three of the 8 bits are used to carry the control information, four are 'parity bits' that allow the video processor to detect and correct a certain level of errors in the transmission of the command words, the remaining bit is always set to 1 to ensure that the command word never has the value 00<sub>H</sub>. The coding scheme used allows the correction of single bit errors (in the 8-bit sequence) and the detection of 2 bit errors. The even parity bits are based on the following relationships:

- 1. An even number of ones in the 4-bit sequence (C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub> and P<sub>0</sub>).

- 2. An even number of ones in the 3-bit sequence (C2, C1, P1).

- 3. An even number of ones in the 3-bit sequence (C2, C0, P2).

- 4. An even number of ones in the 3-bit sequence (C<sub>1</sub>, C<sub>0</sub>, P<sub>3</sub>).

Table 7 shows how the parity bits maybe used to detect and correct 1-bit errors and detect 2-bit errors.

| Line Code            | Nibble X <sub>H</sub> (1 C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> ) | Nibble Y <sub>H</sub> (P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> ) |

|----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| End of Line          | 1000 <sub>2</sub> (8 <sub>H</sub> )                                     | 0000 <sub>2</sub> (0 <sub>H</sub> )                                                  |

| Blank Line (BL)      | 1001 <sub>2</sub> (9 <sub>H</sub> )                                     | 1101 <sub>2</sub> (D <sub>H</sub> )                                                  |

| Black line (BK)      | 1010 <sub>2</sub> (A <sub>H</sub> )                                     | 1011 <sub>2</sub> (B <sub>H</sub> )                                                  |

| Visible Line (VL)    | 1011 <sub>2</sub> (B <sub>H</sub> )                                     | 0110 <sub>2</sub> (6 <sub>H</sub> )                                                  |

| Start of Field (SOF) | 1100 <sub>2</sub> (C <sub>H</sub> )                                     | 0111 <sub>2</sub> (7 <sub>H</sub> )                                                  |

| End of Field (EOF)   | 1101 <sub>2</sub> (D <sub>H</sub> )                                     | 1010 <sub>2</sub> (A <sub>H</sub> )                                                  |

Table 6: Embedded Line Codes (for 4 wire output mode)

| Parity Checks  |                 |                | Comment        |                                                          |

|----------------|-----------------|----------------|----------------|----------------------------------------------------------|

| P <sub>3</sub> | P <sub>2</sub>  | P <sub>1</sub> | P <sub>0</sub> | Comment                                                  |

| ~              | ~               | ~              | ~              | Code word un-corrupted                                   |

| ~              | ~               | V              | ×              | P <sub>0</sub> corrupted, line code OK                   |

| ~              | ~               | ×              | ~              | P <sub>1</sub> corrupted, line code OK                   |

| ~              | ×               | V              | ~              | P <sub>2</sub> corrupted, line code OK                   |

| ×              | ~               | V              | ~              | P <sub>3</sub> corrupted, line code OK                   |

| ×              | ×               | V              | ×              | C <sub>0</sub> corrupted, invert sense of C <sub>0</sub> |

| ×              | ~               | ×              | ×              | C <sub>1</sub> corrupted, invert sense of C <sub>1</sub> |

| ~              | ×               | ×              | ×              | C <sub>2</sub> corrupted, invert sense of C <sub>2</sub> |

|                | All other codes |                |                | 2-bit error in code word.                                |

Table 7: Parity Checking

# 6.2 8-Wire Parallel Mode

If this output mode is selected then the 8-bit pixel data is output on pins DATA[7:0]. The data is valid on the falling edge of the pixel qualification clock, QCK.

### 6.3 4-Wire Parallel Mode

If the 4-Wire parallel mode is selected then a pixel value is output over 2, 4-wire nibbles transmitted over pins DATA[7:4]. A falling edge on QCK will sample a data nibble.

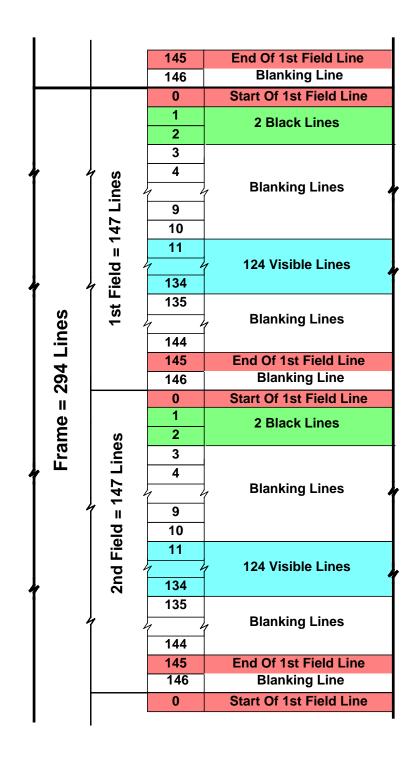

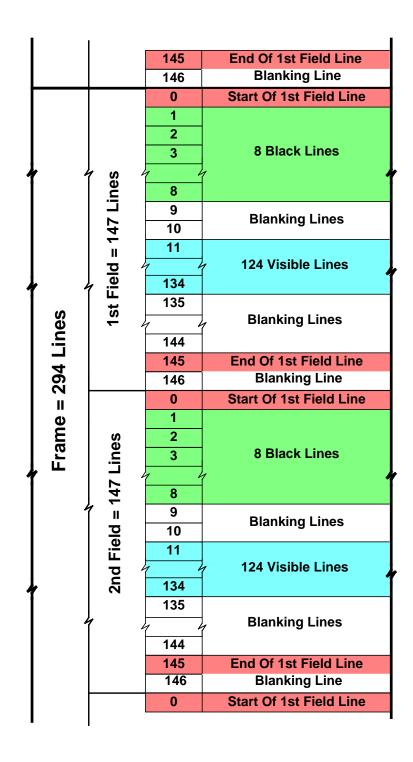

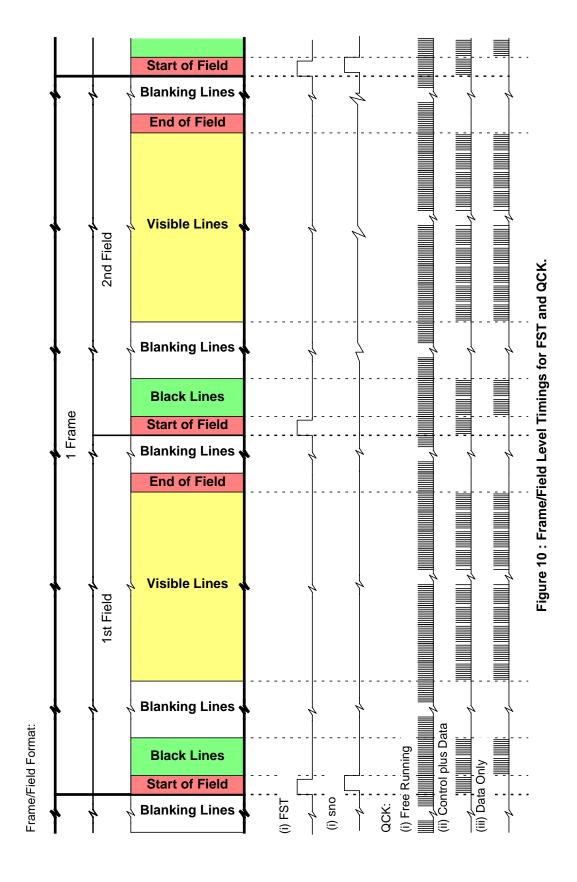

### 6.4 Video Frame Composition

Each frame of video sequence comprises 2 fields. Each field of data is constructed of the following sequence of data lines.

- 1. A start of field line

- 2. A number of black lines

- 3. A number of blank (or dark) lines

- 4. A number active video lines

- 5. An end of field line

- 6. A number of blank or black lines

| Video Format        | QS  | QSIF |  |  |  |

|---------------------|-----|------|--|--|--|

| Extra Black Lines   | On  | Off  |  |  |  |

| 1st Field           |     |      |  |  |  |

| Start of Field Line | 1   | 1    |  |  |  |

| Black Lines         | 8   | 2    |  |  |  |

| Blanking Lines      | 2   | 8    |  |  |  |

| Active Video lines  | 124 | 124  |  |  |  |

| Blanking Lines      | 10  | 10   |  |  |  |

| End of Field Line   | 1   | 1    |  |  |  |

| Blanking Lines      | 1   | 1    |  |  |  |

| Total               | 147 | 147  |  |  |  |

| 2nd Field           |     |      |  |  |  |

| Start of Field Line | 1   | 1    |  |  |  |

| Black Lines         | 8   | 2    |  |  |  |

| Blanking Lines      | 2   | 8    |  |  |  |

| Active Video lines  | 124 | 124  |  |  |  |

| Blanking Lines      | 10  | 10   |  |  |  |

| End of Field Line   | 1   | 1    |  |  |  |

| Blanking Lines      | 1   | 1    |  |  |  |

| Total               | 147 | 147  |  |  |  |

**Table 8: Field and Frame Composition**

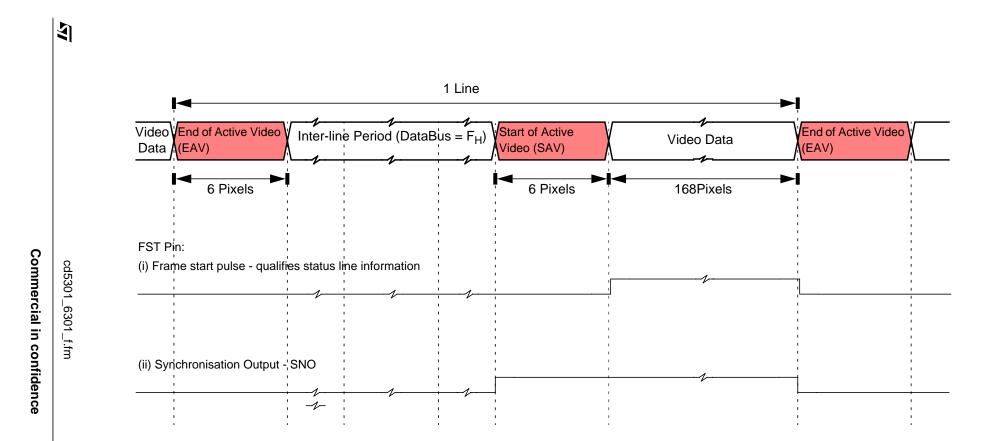

Each line of data starts with an embedded control sequence that identifies the line type (as outlined in). The control sequence is then followed by two bytes that contain a coded line number. The line number sequences starts with the start-of-frame line at  $00_H$  and increments one per line up until the end-of-frame line. Each line is terminated with an end-of-line embedded control sequence. The line start embedded sequences must be used to recognise visible video lines as a number of null bytes may be inserted between successive data lines.

There are two figures (Figure 7 - Figure 8) on the following pages that show line type field construction.

# 6.4.1 Blank lines

18/49

In addition to padding between data lines, actual blank data lines may appear in the positions indicated above. These lines begin

cd5301\_6301\_f.fm

with start-of-blank-line embedded control sequences and are constructed identically to active video lines except that they will contain only blank bytes,  $07_H$ , (expressed as  $01C_H$  in 10bit form).

# 6.4.2 Black line timing

The black lines (which are used for black calibration) are identical in structure to valid video lines except that they begin with a start-of-black line code and contain information from the sensor black lines.

The user can opt to enable extra black lines up to a maximum of 8. The black calibration algorithm always has access to the data contained within these lines whether they are externally enabled or not.

Figure 7: Field and Frame Formats - Extra Black Lines Off

Figure 8: Field and Frame Formats - Extra Black Lines On

## 6.5 Qualifying the Output Data

Data is output from VV5301/VV6301 in a continuous stream. By utilizing signals, like FST, and key events, like the start of a line or the end of line, the user can sample and display the image data. QCK is used to sample the data, as described in the previous section.

Different periods of the frame can be qualified by QCK. The options, which are selected via setup register4 in the serial interface, are as follows:

- 1. QCK disabled, no data qualified (default)

- 2. QCK free running, all data qualified

- 3. QCK qualifies image data only, to include data on black lines currently enabled

- 4. QCK qualifies embedded control sequences as well as image data. The status line data is also qualified with this option.

# 6.5.3 Frame Start Signal, FST

There are 3 modes of operation for the FST pin programmable via the serial interface:

- 1. FST disabled, (default).

- 2. FST enabled, qualifies

- 3. Shutter/Electronic Flash Synchronisation Signal FST rises a the start of the video data in the first black/blank line after the EOF line and falls at the end of data in the SOF line.

The FST output is tri-stated either when OEB is driven high or via the appropriate control bit in the serial interface, (see data\_format register[22]).

Figure 9: Qualification of Output Data (Border Rows and Columns Enabled).

Figure 11: Line Level Timings for FST.

#### 7. Serial Control Bus

### 7.1 General Description

Writing configuration information to the video sensor and reading both sensor status and configuration information back from the sensor is performed via the 2-wire serial interface.

Communication using the serial bus centres around a number of registers internal to the video sensor. These registers store sensor status, set-up, exposure and system information. Most of the registers are read/write allowing the receiving equipment to change their contents. Others (such as the chip id) are read only.

The main features of the serial interface include:

- Broad-cast address to ease setting up multiple camera configurations.

- Variable length read/write messages.

- Indexed addressing of information source or destination within the sensor.

- · Automatic update of the index after a read or write message.

- Message abort with negative acknowledge from the master.

- Byte oriented messages.

The contents of all internal registers accessible via the serial control bus are encapsulated in each start-of-field line.

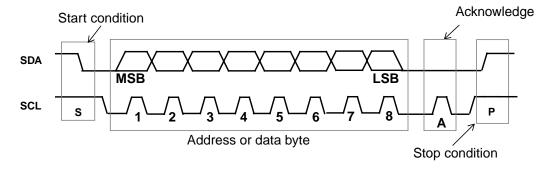

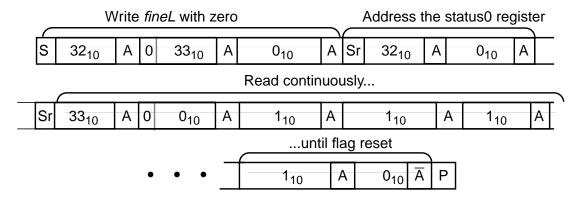

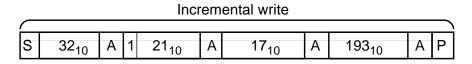

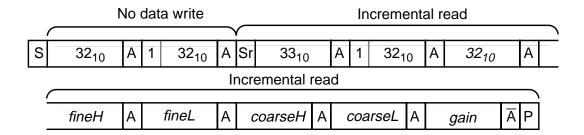

## 7.2 Serial Communication Protocol

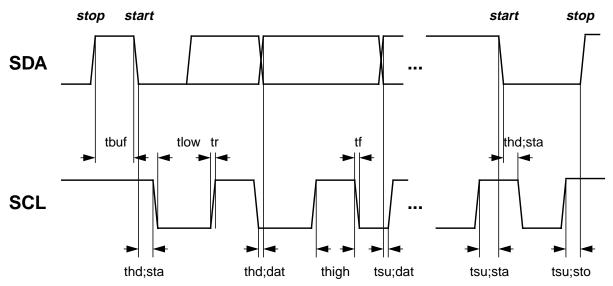

The co- processor or host must perform the role of a communications master and the camera acts as either a slave receiver or transmitter. The communication from host to camera takes the form of 8-bit data with a maximum serial clock video processor frequency of up to 100 kHz. Since the serial clock is generated by the bus master it determines the data transfer rate. Data transfer protocol on the bus is illustrated in Figure 12.

Figure 12: Serial Interface Data Transfer Protocol

### 7.3 Data Format

Information is packed in 8-bit packets (bytes) always followed by an acknowledge bit. The internal data is produced by sampling *sda* at a rising edge of *scl*. The external data must be stable during the high period of *scl*. The exceptions to this are *start* (S) or *stop* (P) conditions when *sda* falls or rises respectively, while *scl* is high.

A message contains at least two bytes preceded by a *start* condition and followed by either a *stop* or *repeated start, (Sr)* followed by another message.

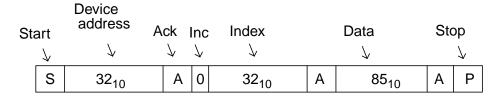

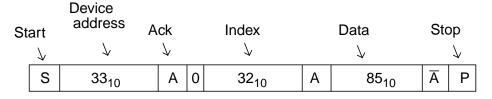

The first byte contains the device address byte which includes the data direction read, (r),  $\sim write$ ,  $(\sim w)$ , bit. The lsb of the address byte indicates the direction of the message. If the lsb is set high then the master will read data from the slave and if the lsb is reset low then the master will write data to the slave. After the r,  $\sim w$  bit is sampled, the data direction cannot be changed, until the next address byte with a new r,  $\sim w$  bit is received.

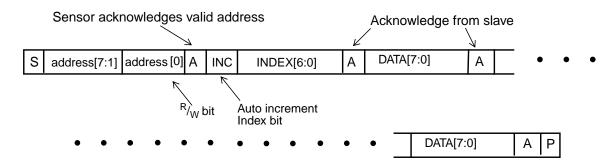

Figure 13: VV5301/VV6301's Serial Interface Address

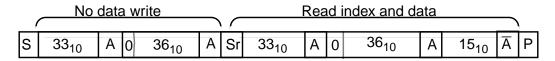

The byte following the address byte contains the address of the first data byte (also referred to as the *index*). The serial interface can address up to 128, byte registers. If the msb of the second byte is set the automatic increment feature of the address index is selected.

Figure 14 : Serial Interface Data Format

## 7.4 Message Interpretation

All serial interface communications with the sensor must begin with a *start* condition. If the *start* condition is followed by a valid address byte then further communications can take place. The sensor will acknowledge the receipt of a valid address by driving the *sda* wire low. The state of the *read/~write* bit (lsb of the address byte) is stored and the next byte of data, sampled from *sda*, can be interpreted.

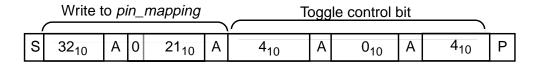

During a write sequence the second byte received is an address index and is used to point to one of the internal registers. The msbit of the following byte is the *index auto increment* flag. If this flag is set then the serial interface will automatically increment the index address by one location after each slave acknowledge. The master can therefore send data bytes continuously to the slave until the slave fails to provide an acknowledge or the master terminates the write communication with a *stop* condition or sends a *repeated start*, (*Sr*). If the auto increment feature is used the master does *not* have to send indexes to accompany the data bytes.

As data is received by the slave it is written bit by bit to a serial/parallel register. After each data byte has been received by the slave, an acknowledge is generated, the data is then stored in the internal register addressed by the current index.

During a read message, the current index is read out in the byte following the device address byte. The next byte read from the slave device are the contents of the register addressed by the current index. The contents of this register are then parallel loaded into the serial/parallel register and clocked out of the device by *scl*.

At the end of each byte, in both read and write message sequences, an acknowledge is issued by the receiving device. Although VV5301/VV6301 is always considered to be a slave device, it acts as a transmitter when the bus master requests a read from the sensor.

At the end of a sequence of incremental reads or writes, the terminal index value in the register will be one *greater* the last location read from or written to. A subsequent read will use this index to begin retrieving data from the internal registers.

A message can only be terminated by the bus master, either by issuing a stop condition, a repeated start condition or by a negative acknowledge after reading a complete byte during a read operation.

28/49

# 7.5 The Programmers Model

There are 128, 8-bit registers within the camera, accessible by the user via the serial interface. They are grouped according to function with each group occupying a 16-byte page of the location address space. There may be up to eight such groups, although this scheme is purely a conceptual feature and not related to the actual hardware implementation, The primary categories are given below:

- Status Registers (Read Only).

- · Setup registers with bit significant functions.

- Exposure parameters that influence output image brightness.

- · System functions and analog test bit significant registers.

Any internal register that can be written to can also be read from. There are a number of read only registers that contain device status information, (e.g. design revision details).

Names that end with H or L denote the most or least significant part of the internal register. Note that unused locations in the H byte are packed with zeroes.

STMicroelectronics sensors that include a 2-wire serial interface are designed with a common address space. If a register parameter is unused in a design, but has been allocated an address in the generic design model, the location is referred to as *reserved*. If the user attempts to read from any of these *reserved or unused* locations a default byte will be read back. In VV5301/VV6301 this data is 12<sub>H</sub>. A write instruction to a reserved (but unused) location is illegal and would not be successful as the device would not allocate an internal register to the data word contained in the instruction.

A detailed description of each register follows. The address indexes are shown as decimal numbers in brackets [....] and are expressed in decimal and *hexadecimal* respectively.

|                     | Serial Register Map for VV5301/VV6301 |          |        |            |                        |                                     |  |  |

|---------------------|---------------------------------------|----------|--------|------------|------------------------|-------------------------------------|--|--|

|                     | · .                                   |          |        |            |                        |                                     |  |  |

| Index <sub>10</sub> | Index <sub>16</sub>                   | Name     | Length | R/W        | Default                | Comments                            |  |  |

|                     | Status Registers - [0-15]             |          |        |            |                        |                                     |  |  |

| 0                   | 0                                     | DevH     | 8      | RO         | 1100 0000 <sub>2</sub> |                                     |  |  |

| 1                   | 1                                     | DevL     | 8      | RO         | 0001 0010 <sub>2</sub> | Reserved                            |  |  |

| 2                   | 2                                     | status0  | 8      | RO         | 0000 1000 <sub>2</sub> | System status information           |  |  |

| 3                   | 3                                     | unused   |        | -          |                        |                                     |  |  |

| 4-6                 | 4-6                                   | unused   | 8      | RO         |                        |                                     |  |  |

| 7                   | 7                                     | frame_av | 8      | RO         |                        | Average value of pixels in a frame. |  |  |

| 8-11                | 8-B                                   | unused   | 8      | RO         |                        |                                     |  |  |

| 12-15               | C-F                                   | unused   |        | -          |                        |                                     |  |  |

|                     |                                       |          | Setu   | ıp Registe | rs - [16-31]           |                                     |  |  |

| 16                  | 10                                    | setup0   | 8      | R/W        | (27 <sub>H</sub> )     | Configure the digital logic         |  |  |

| 17                  | 11                                    | setup1   | 8      | R/W        | (70 <sub>H</sub> )     | Configure the digital logic         |  |  |

| 18                  | 12                                    | setup2   | 8      | R/W        | (1F <sub>H</sub> )     | Pixel counter reset value           |  |  |

| 19                  | 13                                    | setup3   | 8      | R/W        | (0F <sub>H</sub> )     | Exposure control modes              |  |  |

| 20                  | 14                                    | setup4   | 8      | R/W        | (00 <sub>H</sub> )     | FST/QCK options                     |  |  |

| 21-31               | 15                                    | unused   |        | -          |                        |                                     |  |  |

|                     |                                       |          | Expos  | ure Regist | ters - [32-47]         |                                     |  |  |

| 32                  | 20                                    | unused   |        | -          |                        |                                     |  |  |

| 33                  | 21                                    | fine     | 8      | R/W        | 00 <sub>H</sub>        | Fine exposure initially zero        |  |  |

| 34                  | 22                                    | unused   |        | -          |                        |                                     |  |  |

| 35                  | 23                                    | coarse   | 8      | R/W        | 70 <sub>H</sub>        | Coarse exposure                     |  |  |

| 36                  | 24                                    | gain     | 8      | R/W        | 00 <sub>H</sub>        | Gain value                          |  |  |

cd5301\_6301\_f.fm

**Serial Control Bus**

|                     | Serial Register Map for VV5301/VV6301 |          |                 |            |                  |                                                       |  |

|---------------------|---------------------------------------|----------|-----------------|------------|------------------|-------------------------------------------------------|--|

| Index <sub>10</sub> | Index <sub>16</sub>                   | Name     | Length          | R/W        | Default          | Comments                                              |  |

| 37                  | 25                                    | clk_div  | 8               | R/W        | 00 <sub>H</sub>  | Clock division                                        |  |

| 38                  | 26                                    | gn_lim   | 8               | R/W        | 07 <sub>H</sub>  | Maximum allowable gain                                |  |

| 39                  | 27                                    | tl       | 8               | R/W        | 55 <sub>H</sub>  | Lower exposure control threshold.                     |  |

| 40                  | 28                                    | tc       | 8               | R/W        | 64 <sub>H</sub>  | Centre exposure control threshold.                    |  |

| 41                  | 29                                    | th       | 8               | R/W        | 73 <sub>H</sub>  | Upper exposure control threshold.                     |  |

| 42-47               | 2A-2F                                 | unused   |                 | -          |                  |                                                       |  |

|                     |                                       |          | Colo            | ur Registe | rs - [48-79]     |                                                       |  |

| 48-79               | 30-4F                                 | reserved |                 |            |                  |                                                       |  |

|                     |                                       |          | Video Ti        | ming Regi  | sters - [80-103] |                                                       |  |

| 80-103              | 50-67                                 | reserved |                 |            |                  |                                                       |  |

|                     | Text Overlay Registers - [104-107]    |          |                 |            |                  |                                                       |  |

| 104-107             | 68-6B                                 | reserved |                 |            |                  |                                                       |  |

|                     |                                       | S        | erial Interface | Autoload   | Registers - [108 | -111]                                                 |  |

| 108-111             | 6C-6F                                 | reserved |                 |            |                  |                                                       |  |

|                     |                                       |          | Syster          | n Register | s - [112-127]    |                                                       |  |

| 112                 | 70                                    | bdac     | 8               | R/W        |                  | Black Calibration setup                               |  |

| 113                 | 71                                    | b0       | 8               | RO         |                  | Manual override of Black Calibration DAC register, B0 |  |

| 114                 | 72                                    | b1       | 8               | RO         |                  | Manual override of Black Calibration DAC register, B0 |  |

| 115                 | 73                                    | unused   |                 |            |                  |                                                       |  |

| 116                 | 74                                    | tms      | 8               | R/W        |                  | Digital comparator threshold                          |  |

| 117                 | 75                                    | unused   |                 |            |                  |                                                       |  |

| 118                 | 76                                    | cr0      | 8               | R/W        |                  |                                                       |  |

| 119                 | 77                                    | cr1      | 8               | R/W        |                  |                                                       |  |

| 120                 | 78                                    | reserved |                 |            |                  |                                                       |  |

| 120-127             | 79-7F                                 | unused   |                 |            |                  |                                                       |  |

A detailed description of each register follows. The address indexes are shown as binary in brackets.

# 7.5.1 Status Registers - [0 - 15],[0-F]

**Serial Control Bus**

# [0-1],[0-1] -[0-1],[0-1] - DeviceH and DeviceL

These registers provide read only information that identifies the sensor type that has been coded as a 12bit number and a 4bit mask set revision identifier. The initial mask revision identifier is 0 i.e.  $0000_2$ . As the mask set is upgraded the revision identifier will increase, i.e. the second mask set will be  $0001_2$  and so on. The device identification number for VVL301 is 301 i.e. 0001 0010 1101<sub>2</sub>.

| Bit | Function                     | Default           | Comment                                                          |

|-----|------------------------------|-------------------|------------------------------------------------------------------|

| 7:4 | Device type identifier       | 1101 <sub>2</sub> | Least significant 4bits of 12bit code identifying the chip type. |

| 3:0 | Mask set revision identifier | 00002             |                                                                  |

Table 9 : [0],[0] - DeviceL

| Bits | Function               | Default    | Comment                                                         |

|------|------------------------|------------|-----------------------------------------------------------------|

| 7:0  | Device type identifier | 0001_00102 | Most significant 8bits of 12bit code identifying the chip type. |

Table 10: [1],[1] - DeviceH

# [2],[2] - Status0

| Bit | Function                      | Default | Comment                                                                   |

|-----|-------------------------------|---------|---------------------------------------------------------------------------|

| 0   | Exposure value update pending | 0       | New exposure setting sent but not yet consumed by the exposure controller |

| 1   | Unused                        | 0       |                                                                           |

| 2   | Gain value update pending     | 0       | New gain value sent but not yet consumed by the exposure controller       |

| 7:4 | Unused                        | 0       |                                                                           |

Table 11: [2],[2] - Status0

# [7],[7] - [12-15],[E-F] - unused

# 7.5.2 Setup Registers - [16 - 31],[10-1F]

# [16],[10] - Setup 0

Setup 0 register controls some fundamental exposure and output format parameters. Defaults are shown in **bold type.**

| Bit | Function                            | Default | Comment                                                                                         |

|-----|-------------------------------------|---------|-------------------------------------------------------------------------------------------------|

| 0   | Automatic exposure control.  Off/On | 1       | Enables or disables automatic exposure control. Current exposure value is frozen when disabled. |

| 1   | Unused                              | 1       |                                                                                                 |

| 2   | Automatic gain control. Off/On      | 1       | Enables or disables automatic gain control. Current gain value is frozen when disabled.         |

| 4:3 | Unused                              | 002     |                                                                                                 |

| 5   | Data format select.                 | 1       | 0 - 8 wire parallel output  1 - 4 wire parallel output                                          |

| 7:6 | Unused                              | 002     |                                                                                                 |

Table 12 : [16], [10] - Setup0

# [17],[11] - Setup1

Setup 1 register controls registers that are less likely to be modified on a regular basis. The user should note that the border pixels/lines can be disabled/enabled independently from the enabling/disabling of the custom analogue horizontal shift register.

| Bit | Function                                    | Default | Comment                                                                                                                        |

|-----|---------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|

| 0   | Enable additional black lines (3-8)  Off/On | 0       | If enabled extra black lines are visible at device output                                                                      |

| 1   | Unused                                      | 1       |                                                                                                                                |

| 2   | Enable horizontal shuffle mode.  Off/On     | 0       | The contents of the horizontal shift register are shuffled so that all the even columns then all the odd columns are read out. |

Table 13: [17], [11] - Setup1

30/49 cd5301\_6301\_f.fm

#### Bit **Function** Default Comment 5:3 Unused 1102 6 50Hz timing/60Hz timing 1 The sensor will produce field rates either suited to 50Hz or 60Hz (default) operating environments.

7 Unused 0

Table 13: [17], [11] - Setup1

# [19],[13] - Setup3

**Serial Control Bus**

| Bit | Function           | Default | Comment                                                                                                                                         |

|-----|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0 | unused             |         |                                                                                                                                                 |

| 6:5 | Exposure step size | 01      | Selects exposure step size. 1/8 for fast but jerky convergence to 1/64 for slow but smooth convergence.  Default 1/16. See Table 15 for details |

| 7   | Unused             | 0       |                                                                                                                                                 |

Table 14: [19],[13] - Setup3

| Bit 6 | Bit 5 | Step size | Comment |

|-------|-------|-----------|---------|

| 0     | 0     | 1/8       |         |

| 0     | 1     | 1/16      | Default |

| 1     | 0     | 1/32      |         |

| 1     | 1     | 1/64      |         |

Table 15: Exposure step size options

# [20],[14] - Setup4

The data output on the serial wire or the 4/8 wire busses can be qualified by an internally generated clock signal, QCK. The QCK function is assigned a dedicated pin, however the FST pin can also output QCK data, if reconfigured. By default, QCK is disabled. The QCK can free run, qualify the embedded coding sequences and the visible data or the visible data only. FST can also be enabled or disabled, default, or alternatively the FST pin can output a timing signal to synchronise several VV5301/VV6301 sensors or finally the FST pin can output the state of the custom analogue block successive approximation ADC output comparator

| Bit | Function          | Default | Comment                        |

|-----|-------------------|---------|--------------------------------|

| 1:0 | FST/QCK pin modes | 00      | See Table 17 below for details |

| 3:2 | QCK modes         | 00      | See Table 18 below for details |

| 5:4 | unused            |         |                                |

| 7:6 | FST modes         | 00      | See Table 19 below for details |

Table 16 : [20],[14] - fg\_modes

| fg_mod | de[1:0] | FST pin | QCK pin |

|--------|---------|---------|---------|

| 0      | 0       | FST     | QCK     |

Table 17: FST/QCK Pin Selection

cd5301\_6301\_f.fm 31/49

**Serial Control Bus**

| fg_mo | ode[1:0] | FST pin             | QCK pin |  |

|-------|----------|---------------------|---------|--|

| 0     | 1        | FST                 | QCK     |  |

| 1     | 0        | QCK <sub>note</sub> | QCK     |  |

| 1     | 1        | Invert QCKnote      | QCK     |  |

Table 17: FST/QCK Pin Selection

note: The FST pin will always output the free running version of QCK (either inverted or normal)

| fg_mode[3:2] |   | QCK state                                    |

|--------------|---|----------------------------------------------|

| 0 0          |   | Off                                          |

| 0            | 1 | Free Running                                 |

| 1            | 0 | Valid during data and control period of line |

| 1            | 1 | Valid only during data period of line        |

Table 18: QCK Modes

| fg_mode[7:6]] |   | FST pin                                                                  |

|---------------|---|--------------------------------------------------------------------------|

| 0 0           |   | Off                                                                      |

| 0             | 1 | Normal behaviour, FST will qualify the visible pixels in the status line |

| 1             | 0 | Synchronisation out pulse, SNO                                           |

| 1             | 1 | Output ADC comparator output, CPO                                        |

Table 19: FST Modes

# [21-31],[15-1F] - unused

32/49

# Exposure Control Registers [32 - 47],[20-2F]

There is a set of parameters that control the time that the sensor pixels are exposed. The parameters are as follows: fine and coarse exposure time, clock division control and finally gain control. The latter parameter does not affect the integration period rather it amplifies the video signal at the output stage of the sensor core. An internal automatic algorithm will, if enabled, continually monitor the pixel output and then, if required, use this data to correct the current exposure.

Manually changing the divisor applied to the incoming crystal clock can alter the effective integration of the sensor. By slowing the internal clock down the integration period can be increased, i.e. halving the pixel clock frequency will double the integration period.

If the user wishes to use the automatic exposure algorithm, the automatic exposure control (controlling fine and coarse exposure) must be enabled. Additional gain control is optional. It is also possible to change the gain manually via the serial interface even if the exposure is adjusted automatically.

If a user wishes to write an external value to one of the automatic exposure algorithm registers then it is advised that the automatic control for that register be disabled prior to using the serial interface to write the external value.

Note: The external exposure (coarse, fine or gain) values do not take effect immediately. Data from the serial interface is read by the exposure algorithm at the start of a video frame. If the user reads an exposure value via the serial interface then the value reported will be the data as yet unconsumed by the exposure algorithm, because the serial interface logic locally stores all the data written to the sensor.

Between writing the exposure data and the point at which the data is consumed by the exposure algorithm, bit 0 of the status register is set. The gain value is updated a frame later than the coarse and fine exposure parameters. The gain is applied directly

> cd5301\_6301\_f.fm **A**

VV5301 & VV6301

at the video output stage and does not require the long set up time of the coarse and fine exposure settings.

The automatic exposure algorithm uses a set of exposure threshold settings. These thresholds may also be modified by the user to alter the algorithm's performance. The exposure algorithm uses these thresholds in a histogram. The three thresholds divide the histogram into 4 regions, very overexposed, overexposed, underexposed and very underexposed. The pixel data received from the sensor core is compared against the thresholds to determine the accuracy of the current exposure setting. A series of flags are set to describe the outcome of the histogram comparison and the new exposure setting can then be derived.

Each exposure parameter is subject to a maximum setting. The fine exposure setting can be clamped to a fixed value regardless of the decision made by the automatic algorithm. The clamping will occur if the coarse exposure setting exceeds a predetermined value and the clamping has been enabled via the serial interface.

| Bit | Function            | Default                                   | Comment                                    |

|-----|---------------------|-------------------------------------------|--------------------------------------------|

| 7:0 | Fine exposure value | 0000_0000 <sub>2</sub> (00 <sub>H</sub> ) | maximum fine (50Hz mode) = FF <sub>H</sub> |

|     |                     |                                           | maximum fine (60Hz mode) = A8 <sub>H</sub> |

Table 20 : [33],[21] - Fine Exposure Value

| Bit | Function              | Default                                   | Comment                                                |

|-----|-----------------------|-------------------------------------------|--------------------------------------------------------|

| 7:0 | Coarse exposure value | 0111_0000 <sub>2</sub> (70 <sub>H</sub> ) | maximum coarse (50Hz and 60Hz modes) = 91 <sub>H</sub> |

Table 21 : [34],[22] - Coarse Exposure Value

|   | Bit | Function   | Default | Comment                                                        |

|---|-----|------------|---------|----------------------------------------------------------------|

| ı | 2:0 | Gain value | 0       | 8 possible gain states can be written via the serial interface |

Table 22: [36],[24] - Gain Value

All 8 binary codes can be written to the core via the serial interface. Only the 4 thermometer codes 000,001,011 and 111 are selected by the automatic exposure algorithm. The 4 other codes are however still valid and will be evaluated as detailed in the table below. It is clear, from the non-linear relationship between the binary code and the actual gain applied at the analogue output stage, that care should be taken when using non thermometer code gain settings. If the user writes a gain code of 110 (real gain = 1.600) and then enables automatic gain control and the controller then decided to reduce the gain, the new gain value would be 011 (real gain = 4.000) i.e. the effective applied gain at the analogue output stage has actually been increased. Care must be taken when writing manual gain values.

The effective system gain for a given binary gain code is as follows:

| VV5301/6301      |                       |

|------------------|-----------------------|

| Gain binary code | Effective system gain |

| 000              | 1.000                 |

| 001              | 2.000                 |

| 010              | 1.333                 |

| 011              | 4.000                 |

| 100              | 1.143                 |

Table 23: System Gain

47/

VV5301/6301

Gain binary code Effective system gain

101 2.667

110 1.600

111 8.000

Table 23 : System Gain

The *undivided* input crystal clock is used by the clock generator circuitry, elements of the serial interface and a small number of other registers in the design. The remaining digital logic and the analogue circuitry, use internally generated clocks, namely the pixel clock and the faster ADC clocks. These clocks are all slower versions of the crystal clock. The ADC clocks may be up to half the crystal frequency, but can be further divided by factors of 2, 4 or 8. The pixel clock is lower frequency than the ADC clock.

| Bit | Function            | Default | Comment                                       |

|-----|---------------------|---------|-----------------------------------------------|

| 1:0 | Clock divisor value | 0       | Pixel clock = Crystal clock ÷2 <sup>n+1</sup> |

Table 24: [37],[25] - Clock Divisor Value

| Bit | Function   | Default | Comment                                               |

|-----|------------|---------|-------------------------------------------------------|

| 2:0 | Gain limit | 7       | The programmed gain cannot be greater than this value |

Table 25 : [38],[26] - Gain Limit

| Bit | Function                 | Default | Comment |

|-----|--------------------------|---------|---------|

| 7:0 | Exposure lower threshold | 85      |         |

Table 26: [39],[27] - Exposure Lower Threshold

| Bit | Function                  | Default | Comment |

|-----|---------------------------|---------|---------|

| 7:0 | Exposure centre threshold | 100     |         |

Table 27: [40],[28] - Exposure Centre Threshold

| Bit | Function                  | Default | Comment |

|-----|---------------------------|---------|---------|

| 7:0 | Exposure higher threshold | 115     |         |

Table 28: [41],[29] - Exposure Higher Threshold

**Serial Control Bus**

VV5301 & VV6301

# [41-47],[29-2F] - unused

[48-111],[30-6F] - reserved

# System Registers [112-127],[70-7F]

## [112],[70] - Black Calibration Setup Register

The sensor contains an automatic function to help maintain an ideal black level for the video signal. The centre 128 pixels, from the designated black lines are summed, averaged and then compared with a reference, to determine if the black level has to be adjusted. If an adjustment is required then the values of the 2 DAC registers, B0 and B1 - addresses [113-114],[71-72], can be altered to remove any offset in the video black level.

| Bit | Function                                     | Default | Comment                                                                                 |  |

|-----|----------------------------------------------|---------|-----------------------------------------------------------------------------------------|--|

| 1:0 | Black calibration trigger select             | 101     | 00 - Never BCal                                                                         |  |

|     |                                              |         | 01 - Always BCal                                                                        |  |

|     |                                              |         | 10 - BCal if failed monitor                                                             |  |

|     |                                              |         | 11 - BCal if gain has changed                                                           |  |

| 3:2 | Black calibration monitor window             | 00      | 00 - 14.00 to 17.99                                                                     |  |

|     | select (pixel average comparison range)      |         | 01 - 13.00 to 18.99                                                                     |  |

|     | <i>3</i> ,                                   |         | 10 - 12.00 to 19.99                                                                     |  |

|     |                                              |         | 11 - 11.00 to 20.99                                                                     |  |

| 4   | Monitor window size set by serial interface. | 0       | If enabled the monitor window size is set directly by the user via the serial interface |  |

|     |                                              |         | the user via the serial interface                                                       |  |