# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **General Description**

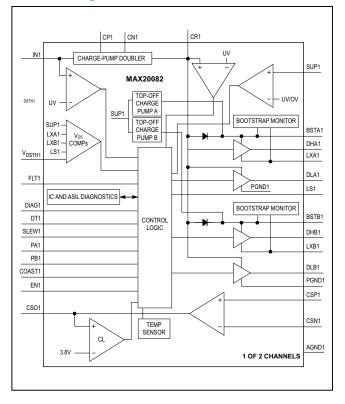

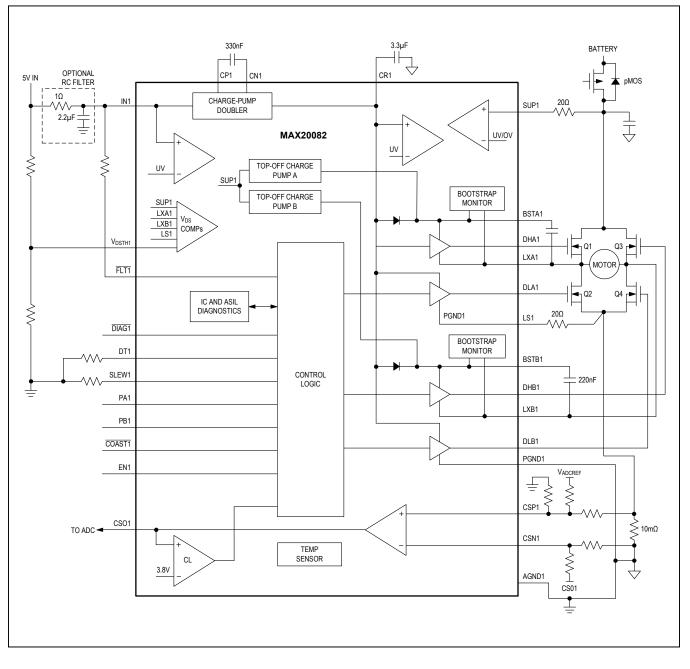

The MAX20082 is a dual, full-bridge controller specifically designed for fault-tolerant automotive applications with high-power inductive loads such as brushed DC motors. The device has two fully independent motor-control channels designed for use with external n-channel power MOSFETs. Each channel operates from a 4.75V to 5.25V input supply voltage range, and is capable of working with motor supply voltages up to 35V.

A charge-pump regulator provides 9.8V gate drive with a 5V input supply voltage. A bootstrap capacitor is used to provide the voltage above the input battery voltage necessary to drive the high-side n-channel MOSFETs in the H-bridge. An internal top-off charge pump for the highside drive allows DC (100% duty cycle) operation.

The device also includes programmable dead time, gatedrive slew rate, and MOSFET short-circuit threshold. The H-bridge can be driven in forward mode (clockwise), reverse mode (counterclockwise), braking mode, and coast mode. In braking mode, both the low-side MOSFETs are turned on (synchronous slow decay). In coast mode, all the MOSFETs in the H-bridge are off (asynchronous fast decay). The power MOSFETs are protected from shoot-through by a resistor-adjustable dead-time circuit.

Each channel also integrates a low-side current-sense amplifier. Used for sensing motor (H-bridge) current, the current-sense amplifier includes an overcurrent-protection circuit to limit the current in the event of motor faults.

Integrated diagnostics provide indication of undervoltage, overtemperature, H-bridge, and pin faults and can be configured to protect the power MOSFETs under most short-circuit conditions. In addition, the device supports implementation in ASIL systems by having two completely redundant H-bridge drivers in one package. The two channels are completely independent and fully redundant, with no shared pins or functions.

The MAX20082 is specified for operation over the full -40°C to +125°C ambient temperature range. The maximum junction temperature is 150°C, with thermal shutdown at 170°C (typ). The device is available in a 56-pin, 14mm x 6.1mm, TSSOP package.

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Comprehensive IC Diagnostics Detect Both IC and H-Bridge Faults, Enhancing System Safety

- Both Channels are Fully Independent Without Any Shared Pins or Circuitry, Providing Complete Redundancy

- Resistor-Programmable Functionality Simplifies

Software Development

- All nFET Operation, Including 100% Duty Cycle, Saves System Cost

#### **Applications**

- Automotive Motor Drivers

- Industrial Motor Drivers

#### **Block Diagram**

19-7047; Rev 0; 8/14

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Absolute Maximum Ratings**

| SUP_, to AGND       | 0.3V to +40V                        |

|---------------------|-------------------------------------|

| LXA_, LXB_, to AGND | 4V to +40V                          |

| BSTA_ to LXA        | 0.3V to +12V                        |

| BSTB_ to LXB        | 0.3V to +12V                        |

| DHA_ to LXA         | 0.3V to V <sub>BST</sub> + 0.3V     |

| DHB_ to LXB         | 0.3V to V <sub>BST</sub> + 0.3V     |

| CR_ to AGND         | 0.3V to +12V                        |

| CN_ to AGND         | 0.3V to (V <sub>IN</sub> + 0.3V)    |

| CP_ to CN           | 0.3∇ to + 6V                        |

| DLA_, DLB_ to AGND  | -0.3V to + (V <sub>CR</sub> + 0.3V) |

| IN_ to AGND         | 0.3V to +6V                         |

| COAST_, PA_, PB_, EN_, DIAG_, V <sub>DSTH</sub> ,              |

|----------------------------------------------------------------|

| SLEW_, DT_, CSO_ to AGND $-0.3V$ to + (V <sub>IN</sub> + 0.3V) |

| FLT_, LS_, CSP_, CSN_ to AGND0.3V to + 6V                      |

| PGND_ to AGND0.3V to 0.3V                                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) TSSOP on |

| Multilayer Board (derate 10.8mW/°C above +70°C)860mW           |

| Operating Ambient Temperature Range40°C to +125°C              |

| Storage Temperature Range55°C to +150°C                        |

| Maximum Junction Temperature+150°C                             |

| Lead Temperature (soldering, 10s)+300°C                        |

| Soldering Temperature (reflow)+260°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Thermal Characteristics (Note 1)

TSSOP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )...........93°C/W

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......21°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(Electrical characteristics valid at  $T_A = T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = 5$ V,  $V_{SUP} = 14$ V,  $V_{EN} = V_{DIAG} = 3.3$ V, DH\_ and DL\_ open, unless otherwise noted.) (Note 2)

| PARAMETER                        | SYMBOL                | CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|-----------------------|--------------------------------------------------------------------------------|------|------|------|-------|

| Input Supply Voltage Range       | V <sub>IN</sub>       |                                                                                | 4.75 |      | 5.25 | V     |

| Input Supply Undervoltage        | V <sub>INPUV</sub>    | Rising                                                                         | 4    | 4.2  | 4.5  | V     |

| Lockout                          | VINUVHYS              | Hysteresis                                                                     |      | 200  |      | mV    |

| Start Un Timor                   |                       | From EN_ going high to $V_{CR} > CR_{UV}ON$ , DIAG_ = low                      |      | 13.5 | 20   |       |

| Start-Up Timer                   | <sup>t</sup> START_UP | From EN_ going high to $V_{CR} > CR_{UV_ON}$ ,<br>DIAG_ = high                 |      | 1.7  | 2    | ms    |

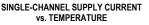

| Cinala Obernal Curalu            |                       | FLT_ and CSO_ pin unconnected                                                  |      | 1.7  | 3    | mA    |

| Single-Channel Supply<br>Current | I <sub>IN_Q</sub>     | $V_{EN} = V_{PA} = V_{PB} = V_{\overline{DIAG}}$ $= V_{\overline{COAST}} = 0V$ |      |      | 10   | μA    |

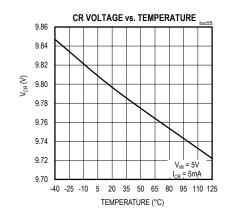

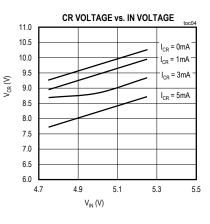

| CR_OUTPUT                        |                       | ·                                                                              |      |      |      |       |

|                                  | N/                    | I <sub>CR</sub> _ = 3mA. C <sub>CP</sub> _ = 330nF, CR_ = 3.3μF                | 9.4  | 9.7  |      | v     |

| CR_ Output Voltage               | V <sub>CR</sub> _     | I <sub>CR</sub> = 3mA, V <sub>IN</sub> = 4.75V                                 | 8.9  | 9.2  |      |       |

|                                  | CR <sub>UV_ON</sub>   | Rising                                                                         | 6.65 | 7    | 7.35 | V     |

| CR_ Undervoltage Lockout         | CR <sub>UV_OFF</sub>  | Hysteresis                                                                     |      | 500  |      | mV    |

| CR_ Charge Timeout               | CR <sub>TO</sub>      | V <sub>CR</sub> _ from 0V to CR <sub>UV_ON</sub>                               | 1.4  | 1.6  | 1.8  | ms    |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Electrical Characteristics (continued)**

(Electrical characteristics valid at  $T_A = T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = 5$ V,  $V_{SUP} = 14$ V,  $V_{EN} = V_{\overline{DIAG}} = 3.3$ V, DH\_ and DL\_ open, unless otherwise noted.) (Note 2)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                                                            | MIN                    | TYP  | MAX | UNITS |

|-------------------------------------|------------------------|---------------------------------------------------------------------------------------|------------------------|------|-----|-------|

| BOOTSTRAP CIRCUIT                   | 1                      |                                                                                       |                        |      |     |       |

| Bootstrap Voltage Drop              | V <sub>BST</sub> _     | V <sub>LX</sub> _= 0V, I <sub>SOURCE</sub> = 10mA                                     | V <sub>CR</sub><br>0.2 |      |     | V     |

| Bootstrap Input Current             | I <sub>BST_</sub>      | V <sub>BST</sub> = 24V, V <sub>LX</sub> = 14V                                         |                        | 0.3  | 0.6 | mA    |

| BST_ Charge Timeout                 | BST <sub>TO</sub>      | V <sub>BST</sub> from 0V to V <sub>BOOSTUV</sub> , COAST rising                       | 0.7                    | 0.8  | 0.9 | ms    |

| Bootstrap Undervoltage              | V <sub>BOOSTUV</sub>   | Rising (V_BSTA_ to V_LXA_or V_BST_B to V_LXB_)                                        | 6.7                    | 7.2  | 7.6 | V     |

| Threshold                           | VBOOSTUVHYS            | Hysteresis (V_BSTA_ to V_LXA_or V_BST_B to V_LXB_)                                    |                        | 1    |     | V     |

| Top-Off Charge-Pump<br>Enable Delay | T <sub>TO_EN_DLY</sub> | PA_, PB_ rising                                                                       | 0.5                    | 0.6  | 0.7 | ms    |

| GATE DRIVE                          |                        | -                                                                                     | _                      |      |     |       |

| Output-Voltage High                 | New men                | $V_{BST_}$ = 9.5V, I <sub>SOURCE</sub> = 10mA,<br>R <sub>SLEW_</sub> = 10kΩ           | 9.1                    | 9.3  |     | v     |

| DH_ to LX_                          | V <sub>DH_HIGH</sub>   | V <sub>BST</sub> = unconnected, V <sub>CR</sub> = 9.8V,<br>I <sub>SOURCE</sub> = 25μA | 6.6                    | 7.7  |     | v     |

| Output-Voltage Low<br>DH_ to LX_    | V <sub>DH_LOW</sub>    | I <sub>SINK</sub> = 10mA                                                              |                        | 0.2  | 0.5 | V     |

| Output-Voltage High<br>DL_ to PGND_ | V <sub>DL_HIGH</sub>   | $I_{SOURCE}$ = 10mA, R <sub>SLEW</sub> = 10kΩ,<br>V <sub>CR</sub> = 9.5V              | 9.1                    | 9.3  |     | v     |

| Output-Voltage Low<br>DL_ to PGND_  | V <sub>DL_LOW</sub>    | I <sub>SINK</sub> = 10mA                                                              |                        | 0.2  | 0.5 | V     |

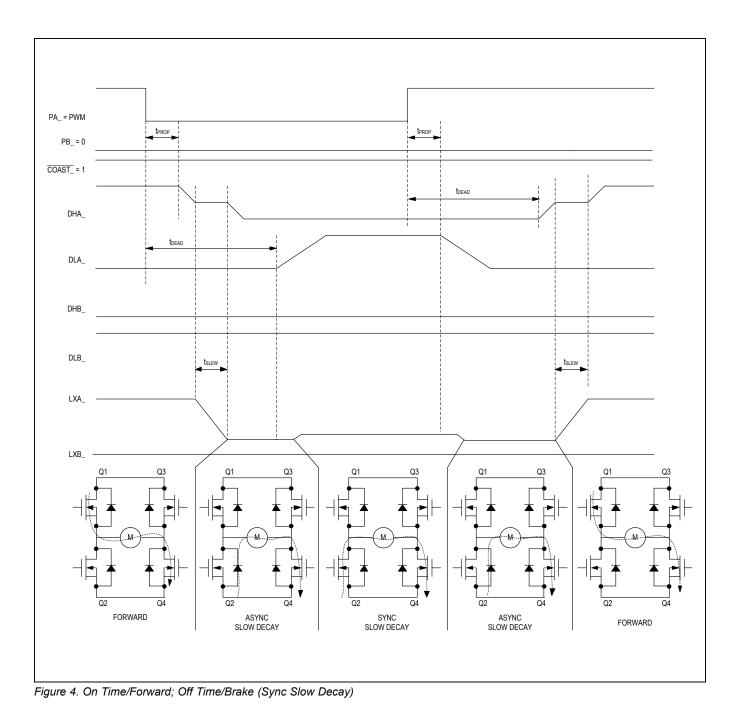

| Turn-Off Propagation Delay          | tOFF                   | See Figure 4 for timing characteristics                                               | 60                     | 100  | 150 | ns    |

| Turn-On Propagation Delay           | t <sub>ON</sub>        | See Figure 4 for timing characteristics                                               | 60                     | 100  | 150 | ns    |

| Propagation Delay<br>Matching       |                        |                                                                                       |                        | 10   |     | ns    |

|                                     |                        | $R_{DT}$ = 10k $\Omega$ (see Figure 4 for timing characteristics)                     |                        | 370  |     |       |

| Dead Time                           | <b>t</b>               | $R_{DT}$ = 40k $\Omega$ (see Figure 4 for timing characteristics)                     |                        | 1100 |     |       |

|                                     | <sup>t</sup> DEAD      | $R_{DT}$ = 100k $\Omega$ (see Figure 4 for timing characteristics)                    | 2500                   |      | ns  |       |

|                                     |                        | $R_{DT}$ = 200k $\Omega$ (see Figure 4 for timing characteristics)                    |                        | 5000 |     |       |

|                                     |                        | R <sub>SLEW</sub> _= 10kΩ                                                             |                        | 40   |     | mA    |

| Slew Current                        | $\frac{-}{8}$          |                                                                                       | 8                      |      | mA  |       |

|                                     |                        | $R_{SLEW} = 200 k\Omega$                                                              |                        | 2    |     | mA    |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Electrical Characteristics (continued)**

(Electrical characteristics valid at  $T_A = T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = 5$ V,  $V_{SUP} = 14$ V,  $V_{EN} = V_{\overline{DIAG}} = 3.3$ V, DH\_ and DL\_ open, unless otherwise noted.) (Note 2)

| PARAMETER                                    | SYMBOL                 | CONDITIONS                                       | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|------------------------|--------------------------------------------------|------|------|------|-------|

| CURRENT-SENSE AMPLIFI                        | ER                     |                                                  |      |      |      |       |

| Input Common-Mode<br>Voltage Range           | CMVR                   |                                                  | 0    |      | 3    | V     |

| Input Offset Voltage                         | V <sub>OFF</sub>       |                                                  | -1.5 |      | +1.5 | mV    |

| Input Bias Current                           | IBIAS                  |                                                  |      | 200  | -600 | nA    |

| Input Offset Current                         | I <sub>OFF</sub>       |                                                  |      | 20   |      | nA    |

| Differential DC Voltage<br>Gain              |                        | $R_{CSO}$ = 2k $\Omega$                          | 90   | 105  |      | dB    |

| Input Capacitance                            | C <sub>CS_IN</sub>     |                                                  |      | 5    |      | pF    |

| Output Voltage Range                         | V <sub>CSO</sub> _     | $I_{CSO}$ = ±3mA                                 | 0.5  |      | 4.5  | V     |

| Output Sink Current                          | I <sub>CSOsink</sub>   | V <sub>CSO</sub> = 0V                            | 10   |      | 50   | mA    |

| Output Source Current                        | ICSOSOURCE             | $V_{\rm CSO}$ = 5V                               | 14   |      | 54   | mA    |

| Output Slew Rate                             | SR                     | Gain > 10, C <sub>LOAD</sub> = 100pF             |      | 10   |      | V/µs  |

| DC Common-Mode<br>Rejection                  | CMR                    |                                                  | 81   | 100  |      | dB    |

| Gain-Bandwidth Product                       | GBW                    | C <sub>LOAD</sub> = 100pF                        |      | 30   |      | MHz   |

| Phase Margin                                 | SR                     | C <sub>LOAD</sub> = 100pF, gain = 10             |      | 66   |      | 0     |

| OVERCURRENT PROTECT                          | ION                    |                                                  | -1   |      |      |       |

| Overcurrent Threshold                        | V <sub>OC</sub>        | V <sub>CSO</sub> _rising                         | 3.5  | 3.75 | 4    | V     |

| Overcurrent Threshold<br>Hysteresis          | V <sub>OC_HYS</sub>    |                                                  |      | 0.2  |      | V     |

| V <sub>DS</sub> PROTECTION                   |                        |                                                  | •    |      |      |       |

| V <sub>DSTH</sub> Input Voltage<br>Range     | V <sub>DS_RNG</sub>    |                                                  | 0.2  |      | 2    | V     |

| V <sub>DSTH</sub> _Accuracy                  | V <sub>DS_ACC</sub>    | V <sub>DSTH</sub> = 0.5V                         | -50  |      | -60  | mV    |

| V <sub>DSTH</sub> Input Current              | V <sub>DSTH</sub>      |                                                  |      | 0.1  | 1    | μA    |

| V <sub>DSTH_</sub> Disable Voltage           | V <sub>DS_DIS</sub>    |                                                  | 2.6  |      |      | V     |

| V <sub>DSTH</sub> Fault Blanking<br>Time     | t <sub>VDS_BLANK</sub> | From dead time elapsed                           | 12   | 15   | 18   | μs    |

| V <sub>DSTH</sub> _Comp Propagation<br>Delay | tvds_del               | From fault time elapsed, 100mV overdrive         |      | 1    |      | μs    |

| LX_ Input Current                            | I <sub>LX</sub>        | $V_{EN}$ = 0V, $V_{LX}$ = 0 to 16V, no switching |      |      | 250  | μA    |

| SUP_Input Current                            | I <sub>SUP</sub> _     |                                                  |      | 50   | 100  | μA    |

| LS_ Input Current                            |                        |                                                  |      |      | 30   | μA    |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Electrical Characteristics (continued)**

(Electrical characteristics valid at  $T_A = T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = 5$ V,  $V_{SUP} = 14$ V,  $V_{EN} = V_{DIAG} = 3.3$ V, DH\_ and DL\_ open, unless otherwise noted.) (Note 2)

| PARAMETER                              | SYMBOL                | CONDITIONS                                | MIN  | TYP  | MAX | UNITS |

|----------------------------------------|-----------------------|-------------------------------------------|------|------|-----|-------|

| SUP_INPUT PROTECTION                   |                       |                                           |      |      |     |       |

| Overvoltage Blanking Time              | <sup>t</sup> BLANK_OV |                                           | 350  | 400  | 450 | ms    |

| SUP_Undervoltage                       | SUPUV                 | Rising                                    | 4.2  | 4.6  | 5   | V     |

| Lockout                                | SUP <sub>UV_HYS</sub> | Hysteresis                                |      | 300  |     | mV    |

|                                        | SUPOV                 | Rising, more than t <sub>BLANK_OV</sub>   | 35   | 36.5 | 38  | V     |

| SUP_ Overvoltage Lockout               | SUP <sub>OV_HYS</sub> | Hysteresis                                |      | 1.2  |     | V     |

| THERMAL PROTECTION                     |                       |                                           |      |      |     |       |

| Overtemperature Fault                  | T <sub>JFT_R</sub>    | Rising                                    |      | 170  |     | °C    |

| Threshold                              | T <sub>JFT_F</sub>    | Falling                                   |      | 145  |     |       |

| FAULT FLAG                             |                       |                                           |      |      |     |       |

| Fault Output, Low State                | V <sub>FLT_LOW</sub>  | I <sub>SINK</sub> = 1mA                   |      |      | 0.3 | V     |

| Fault Output Leakage, High State       | I <sub>FLT_HIGH</sub> | V <sub>FLT_</sub> = 5V -1                 |      | +1   | μA  |       |

| Fault Class 1                          | %                     |                                           |      | 12.5 |     | %     |

|                                        | <sup>%</sup> FLT_1    | DIAG_ low during pin-to-pin check routine | 62.5 |      | 70  |       |

| Fault Class 2                          | %FLT_2                |                                           |      | 25   |     | %     |

| Fault Class 3                          | %FLT_3                |                                           |      | 50   |     | %     |

| Fault Class 4                          | <sup>%</sup> FLT_4    |                                           |      | 75   |     | %     |

| Fault Class 5                          | %FLT_5                |                                           |      | 87.5 |     | %     |

| Fault Frequency                        | f <sub>FLT</sub>      |                                           | 550  | 625  | 700 | kHz   |

| EN_, COAST_, PA_, PB_, ar              | nd DIAG_LOGIC         | INPUTS                                    |      |      |     |       |

| Input High Voltage                     | IN <sub>VIH</sub>     |                                           | 2    |      |     | V     |

| Input Low Voltage                      | IN <sub>VIL</sub>     |                                           |      |      | 0.7 | V     |

| Input Leakage Current                  | IN <sub>LKG</sub>     | Input voltage from 0 to 5.5V -1 +         |      | +1   | μA  |       |

| EN_ Deglitch Time                      | t <sub>RES</sub>      | Note 3         7         10         13    |      | 13   | μs  |       |

| EN_ Pulldown Resistor                  | EN_RES                |                                           |      | 50   |     | kΩ    |

| EN_ Low Time to Enter<br>Shutdown Mode | <sup>t</sup> SHDW     | Note 4                                    | 0.8  | 1    | 1.2 | ms    |

**Note 2:** Limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: Minimum time EN\_ has to be low in order to enter reset state.

Note 4: Minimum time EN\_ has to stay low after a power-up in order to enter shutdown mode.

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

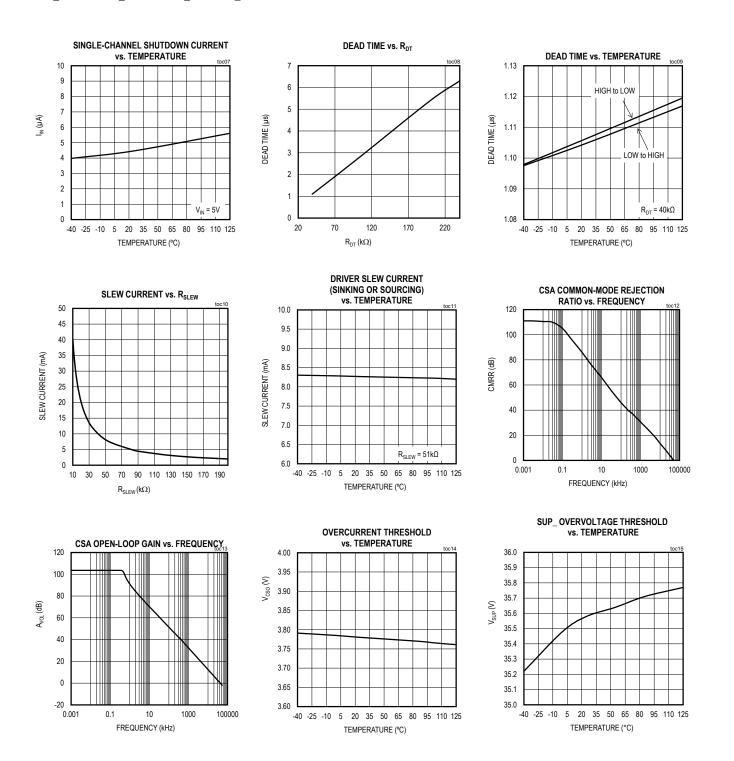

### **Typical Operating Characteristics**

(V<sub>IN\_</sub> = 5V, V<sub>SUP\_</sub> = 14V, V<sub>EN\_</sub> = V<sub>DIAG\_</sub> = 3.3V, unless otherwise noted.)

### Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

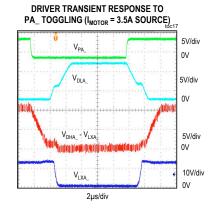

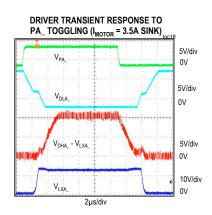

#### **Typical Operating Characteristics (continued)**

(V<sub>IN\_</sub> = 5V, V<sub>SUP\_</sub> = 14V, V<sub>EN\_</sub> = V<sub>DIAG\_</sub> = 3.3V, unless otherwise noted.)

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 5V, V<sub>SUP</sub> = 14V, V<sub>EN</sub> = V<sub>DIAG</sub> = 3.3V, unless otherwise noted.)

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

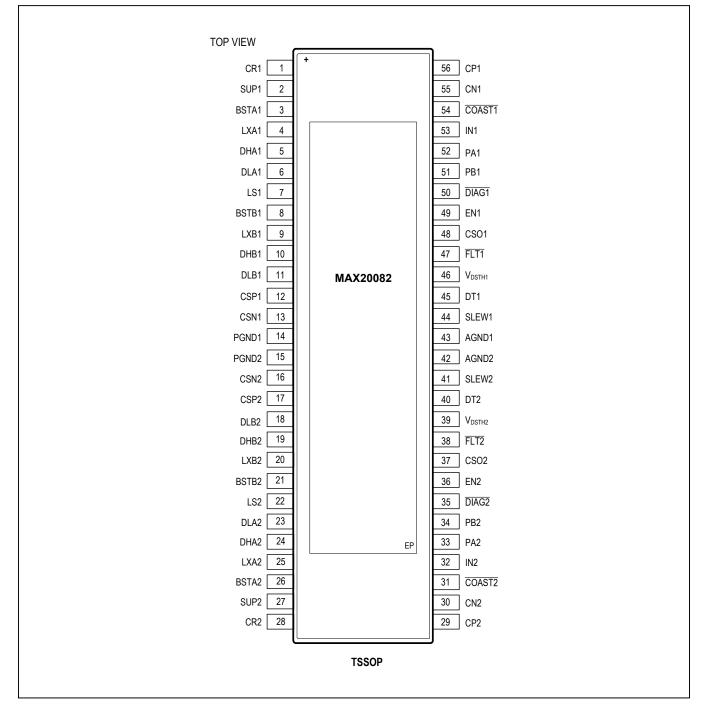

# **Pin Configuration**

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

### **Pin Description**

| PIN | NAME   | FUNCTION                                             |  |  |  |

|-----|--------|------------------------------------------------------|--|--|--|

| 1   | CR1    | Nominal 10V Supply Voltage for the Gate Drivers      |  |  |  |

| 2   | SUP1   | High-Side Common Drain Connection and Sense          |  |  |  |

| 3   | BSTA1  | Bootstrap Capacitor Connection for High-Side Drive A |  |  |  |

| 4   | LXA1   | Motor Connection A                                   |  |  |  |

| 5   | DHA1   | High-Side Gate Drive A                               |  |  |  |

| 6   | DLA1   | Low-Side Gate Drive A                                |  |  |  |

| 7   | LS1    | Low-Side Common Source Connection                    |  |  |  |

| 8   | BSTB1  | Bootstrap Capacitor Connection for High-Side Drive B |  |  |  |

| 9   | LXB1   | Motor Connection B                                   |  |  |  |

| 10  | DHB1   | High-Side Gate Drive B                               |  |  |  |

| 11  | DLB1   | Low-ide Gate Drive B                                 |  |  |  |

| 12  | CSP1   | Positive Input Current Sense                         |  |  |  |

| 13  | CSN1   | Negative Input Current Sense                         |  |  |  |

| 14  | PGND1  | Power Ground                                         |  |  |  |

| 15  | PGND2  | Power Ground                                         |  |  |  |

| 16  | CSN2   | Negative Input Current Sense                         |  |  |  |

| 17  | CSP2   | Positive Input Current Sense                         |  |  |  |

| 18  | DLB2   | Low-Side Gate Drive B                                |  |  |  |

| 19  | DHB2   | High-Side Gate Drive B                               |  |  |  |

| 20  | LXB2   | Motor Connection B                                   |  |  |  |

| 21  | BSTB2  | Bootstrap Capacitor Connection for High-Side Drive B |  |  |  |

| 22  | LS2    | Low-Side Common Source Connection                    |  |  |  |

| 23  | DLA2   | Low-Side Gate Drive A                                |  |  |  |

| 24  | DHA2   | High-Side Gate Drive A                               |  |  |  |

| 25  | LXA2   | Motor Connection A                                   |  |  |  |

| 26  | BSTA2  | Bootstrap Capacitor Connection for High-Side Drive A |  |  |  |

| 27  | SUP2   | High-Side Common Drain Connection and Sense          |  |  |  |

| 28  | CR2    | Nominal 10V Supply Voltage for the Gate Drivers      |  |  |  |

| 29  | CP2    | Charge-Pump Doubler Capacitor Connection P           |  |  |  |

| 30  | CN2    | Charge-Pump Doubler Capacitor Connection N           |  |  |  |

| 31  | COAST2 | Active-Low H-Bridge Disable Input                    |  |  |  |

| 32  | IN2    | 5V Input Supply                                      |  |  |  |

| 33  | PA2    | Logic Control Input A                                |  |  |  |

| 34  | PB2    | Logic Control Input B                                |  |  |  |

| 35  | DIAG2  | Diagnostic Input                                     |  |  |  |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

### **Pin Description (continued)**

| PIN | NAME               | FUNCTION                                    |

|-----|--------------------|---------------------------------------------|

| 36  | EN2                | Enable Input                                |

| 37  | CSO2               | Input Current-Sense Amplifier Output        |

| 38  | FLT2               | Fault Flag Open-Drain Output                |

| 39  | V <sub>DSTH2</sub> | Drain-to-Source Fault-Threshold Level Input |

| 40  | DT2                | Dead-Time Resistor Connection               |

| 41  | SLEW2              | Slew-Time Resistor Connection               |

| 42  | AGND2              | Analog Ground                               |

| 43  | AGND1              | Analog Ground                               |

| 44  | SLEW1              | Slew-Time Resistor Connection               |

| 45  | DT1                | Dead-Time Resistor Connection               |

| 46  | V <sub>DSTH1</sub> | Drain-to-Source Fault-Threshold Level Input |

| 47  | FLT1               | Fault Flag Open-Drain Output                |

| 48  | CSO1               | Input Current-Sense Amplifier Output        |

| 49  | EN1                | Enable Input                                |

| 50  | DIAG1              | Diagnostic Input                            |

| 51  | PB1                | Logic Control Input B                       |

| 52  | PA1                | Logic Control Input A                       |

| 53  | IN1                | 5V Input Supply                             |

| 54  | COAST1             | Active-Low H-Bridge Disable Input           |

| 55  | CN1                | Charge-Pump Capacitor Connection N          |

| 56  | CP1                | Charge-Pump Capacitor Connection P          |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Detailed Description**

The MAX20082 is a dual, full-bridge controller specifically designed for use in fault-tolerant automotive applications, with high-power inductive loads such as brushed DC motors. The device has two fully independent motor-control channels designed for use with external n-channel power MOSFETs. Each channel operates from a 4.75V to 5.25V input supply voltage range, and is capable of working with motor supply voltages up to 35V.

A charge-pump regulator provides 9.8V gate drive with a 5V input supply voltage. A bootstrap capacitor is used to provide the voltage above the input battery voltage necessary to drive the high-side n-channel MOSFETs in the H-bridge. An internal top-off charge pump for the highside drive allows DC (100% duty cycle) operation.

The device also includes programmable dead time, gatedrive slew rate, and MOSFET short-circuit threshold. The H-bridge can be driven in forward mode (clockwise), reverse mode (counterclockwise), braking mode, and coast mode. In braking mode, both the low-side MOSFETs are turned on (synchronous slow decay). In coast mode, all the MOSFETs in the H-bridge are off (asynchronous fast decay). The power MOSFETs are protected from shoot-through by a resistor-adjustable dead time.

Each channel also integrates a low-side current-sense amplifier. Used for sensing-motor (H-bridge) current, the current-sense amplifier includes an overcurrentprotection circuit to limit the current in the event of motor faults.

Integrated diagnostics provide indication of undervoltage, overtemperature, H-bridge, and pin faults and can be configured to protect the power MOSFETs under most short-circuit conditions. In addition, the device supports implementation in ASIL systems by having two completely redundant H-bridge drivers in one package. The two channels are completely independent and fully redundant, with no shared pins or functions. The device is specified for operation over the full -40°C to +125°C ambient temperature range. The maximum junction temperature is +150°C, with thermal shutdown at +170°C (typ). The device is available in a 56-pin 14mm x 6.1mm TSSOP package.

#### Input Supply

Individual 5V power-supply connections, isolated with fuses, should be provided to the device in order to guarantee fault isolation. Decouple each supply with a 2.2 $\mu$ F ceramic capacitor connected close to the IN\_pins and ground pins. An RC filter, consisting of a 1 $\Omega$  resistor in series with a 2.2 $\mu$ F connected to AGND, is needed to prevent supply line transients from triggering undesired UVLO faults. The device operates within specified parameters with an input supply from 4.75 to 5.25 V.

#### Input Supply Undervoltage

The device includes undervoltage-lockout circuitry (UVLO) on the IN\_ pins. Input supply voltages of less than 4.25V inhibit operation of the device by turning off the driver outputs (motor in coast) and CR\_ charge pump.

#### **Charge Pump**

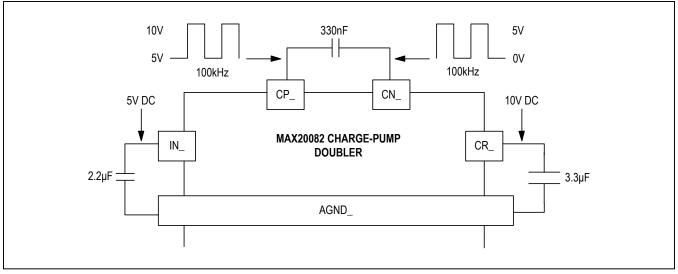

A charge-pump doubler provides the voltage required to drive the switching MOSFETs in the H-bridge. The charge-pump boost converter doubles the input supply voltage (IN\_) through a pump capacitor connected between the CP\_ and CN\_ pins. This capacitor should typically be a 330nF ceramic type. The switching frequency of the charge pump is set at 100kHz.

The regulated voltage is available on the CR\_ pin. Connect a  $3.3\mu$ F ceramic capacitor between CR\_ and AGND\_ to provide the transient charging current to the low-side drivers and the bootstrap capacitors. The charge pump features undervoltage-lockout circuitry that turns off the driver outputs (motor in coast) and CR charge pump when the CR\_ voltage is lower than 7V (typ). See Figure 1.

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

Figure 1. Charge-Pump Doubler

#### **Top-Off Charge Pump**

A top-off charge pump maintains the gate voltage on the external FETs during 100% duty-cycle operation. It is a low-current trickle pump and operates only when the corresponding high-side FET has been on for at least 0.6ms (typ). Without the top-off charge pump, this current would be drawn from the bootstrap capacitor causing it to discharge. The charge pump provides sufficient current to ensure that the bootstrap voltage is maintained close to twice the IN\_ voltage. The dynamic charge required to turn on the external FETs is provided by the bootstrap capacitor. The top-off charge pump only provides the charge required to compensate for any leakage current that occurs on the high-side once the FET is on.

#### Low-Side Gate Drivers

The gate drivers are controlled by the logic inputs (PA\_ and PB\_). The low-side drivers are powered by the charge-pump output voltage on CR\_. DLA\_ controls the low-side FET whose drain is connected to LXA\_ and DLB\_ controls the low-side FET whose drain is connected to LXB\_. DLA\_ goes low to turn off the low-side FET whose drain is connected to LXA\_ and DLB\_ goes low to turn off the low-side FET whose drain is connected to LXB\_.

The rise and fall times can be controlled by a resistor on the SLEW\_ pin and are designed to be symmetrical. Additional increase in the slew times can be achieved by adding external resistors in series with the connection to the external FET gate. The dead time is controlled by a resistor on the DT\_ pin and is also symmetrical.

#### Low-Side MOSFET Drain Connection

The LXA\_ and LXB\_ pins are directly connected to the motor. These pins should be connected to the negative side of the bootstrap capacitors and are the negative rail connection for the high-side drivers. The discharge current from the high-side gate capacitance flows through these connections so a low-impedance connection is needed to the MOSFET bridge.

### Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **High-Side Gate Drivers**

The high-side gate drive outputs (DHA\_ and DHB\_) are used to drive the high-side FETs in the H-bridge. Connect the external FET gates as close as possible to the DHA\_ and DHB\_ pins.

Both the rise/fall times can be controlled by the resistor on the SLEW\_ pin. Additional gate-drive resistors can be added to increase the slew times beyond what is programmed on the SLEW\_ pin. The dead time is controlled by the resistor on the DT\_ pin and is symmetrical.

#### **Bootstrap Capacitor Connections**

These are the high-side connections for the bootstrap capacitors and are the positive supply for the high-side gate drives. The bootstrap capacitors are charged to approximately the CR\_ voltage when the associated output LXA\_ or LXB\_ terminal is low.

When the LXA\_ or LXB\_ output swings high, the charge on the bootstrap capacitor causes the voltage at the corresponding BSTA\_ or BSTB\_ terminal to rise with the output to provide the boosted gate voltage needed to drive the high-side MOSFETs.

Undervoltage circuitry monitors the voltage on the bootstrap capacitors and turns on the H-bridge low-side FETs (see the faults description) if this voltage is lower than 60% of the CR\_ voltage. A typical bootstrap capacitor value of 330nF is advised.

#### **Dead-Time Programming**

Dead time is defined as the time between the high/low side starting to turn off and the complementary side starting to turn on. Dead time is required to prevent shoot-through in the MOSFET bridge when the high- or low-side FET is turned off and the complementary low- or high-side FET is turned on. Set the dead time for all the phases in one channel by a single resistor on the DT\_ pin.

The voltage on the DT\_ pin is regulated to  $1V \pm 3\%$  when a resistor greater than  $10k\Omega$  is connected from this pin to AGND . The dead time is programmed by the current

through the DT\_ resistor, within a range between 370ns to  $5\mu$ s. The current flowing into the resistor on the DT\_ pin is given by:

$$I_{DT} = 1/R_{DT}$$

where R<sub>DT</sub> is the resistor on the DT pin. For R<sub>DT</sub> values between 10k $\Omega$  and 200k $\Omega$  at 25°C, the nominal value of the dead time (t<sub>DEAD</sub>) is given by:

$t_{DEAD}(R_{DT}) = 25 \times R_{DT}$  (k) + 100ns

#### **Slew-Time Programming**

The gate pullup or pulldown current for all the FETs is programmed by a resistor on the SLEW\_ pin. This results in controlled LX\_ rise and fall times, which are symmetrical and equivalent for all the FETs in the H-bridge. The voltage on the slew pin is regulated to 1V  $\pm$ 3% when a resistor greater than 10k $\Omega$  is connected from this pin to AGND\_.

The slew current is programmed within the 40mA and 2mA range. The current flowing into the resistor on the SLEW\_ pin is given by:

$$I_{SLEW} = 1/R_{SLEW}$$

where  $R_{SLEW}$  is the resistor on the SLEW\_ pin. For  $R_{SLEW}$  values between  $10k\Omega$  and  $200k\Omega$  at  $25^\circ\text{C}$ , the nominal value of the slew current ( $I_{SLEW}$ ) is given by:

$$I_{SLEW}$$

(R<sub>SLEW</sub>) = 400/R<sub>SLEW</sub> (k) mA

Slew time can be determined with the following formula, where  $Q_{GD}$  is the gate drain charge of the external nMOS:

$$t_{SLEW} = Q_{GD} (nF)/I_{SLEW} (mA)$$

#### Enable

When EN\_ is low, the device is in shutdown mode and the maximum current drawn by each half of the device is less than  $10\mu$ A. To enter shutdown, hold EN\_ low for at least 1.2ms.

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Phase Control**

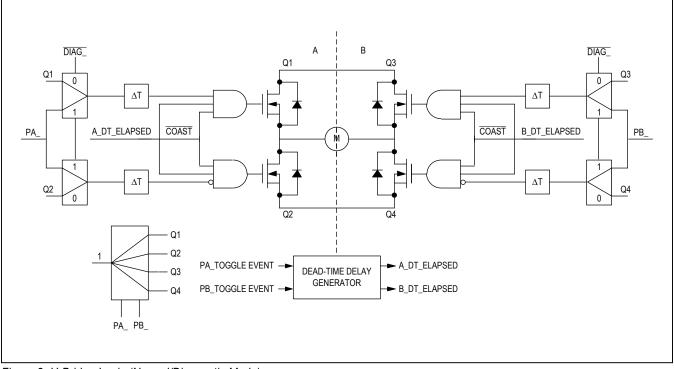

The COAST\_, PA\_, and PB\_ logic inputs allow motor control through a single-bit PWM digital signal. Depending on the logic configuration of the PA\_ and PB\_ inputs, the  $\mu$ C can select the direction of the motor and the current-decay mode during the off time (see Figure 2, Figure 3, and Table 1).

- PA\_ (PB\_) 0  $\rightarrow$  1 and  $\overline{\text{COAST}}$  = 1:

- 1) Q2 (Q4) is turned off and dead-time delay starts.

- 2) When dead-time delay elapses, Q1 (Q3) is turned on.

- PA\_ (PB\_) 1  $\rightarrow$  0 and  $\overline{\text{COAST}}$  =1:

- 1) Q1 (Q3) is turned off and dead-time delay starts.

- 2) When dead-time delay elapses, Q2 (Q4) is turned on.

Figure 2. H-Bridge Logic (Normal/Diagnostic Mode)

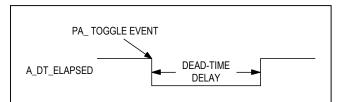

Figure 3. A\_DT\_Elapsed Signal Used in Dead-Time Generation

#### **Table 1. Phase Control**

| PA_ (PB_) | COAST_ | Q1 (Q3) | Q2 (Q4) |

|-----------|--------|---------|---------|

| 1         | 1      | On      | Off     |

| 0         | 1      | Off     | On      |

| X         | 0      | Off     | Off     |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

### Table 2. H-Bridge Application

| PA_ | PB_ | COAST_ | ON TIME                | OFF TIME                |

|-----|-----|--------|------------------------|-------------------------|

| PWM | 0   | 1      | Forward (Q1 and Q4 on) | LS brake (Q2 and Q4 on) |

| 1   | PWM | 1      | Forward (Q1 and Q4 on) | HS brake (Q1 and Q3 on) |

| PWM | PWM | 1      | Forward (Q1 and Q4 on) | Reverse (Q2 and Q3 on)  |

| 0   | PWM | 1      | Reverse (Q2 and Q3 on) | LS brake (Q2 and Q4 on) |

| PWM | 1   | 1      | Reverse (Q2 and Q3 on) | HS brake (Q1 and Q3 on) |

| PWM | PWM | 1      | Reverse (Q2 and Q3 on) | Forward (Q1 and Q4 on)  |

### Table 3. Truth Table for External MOSFET Control

| PA_ | PB_ | COAST_ | DIAG_ | Q1  | Q2  | Q3  | Q4  | H-BRIDGE STATE           |

|-----|-----|--------|-------|-----|-----|-----|-----|--------------------------|

| 0   | 0   | 1      | 1     | Off | On  | Off | On  | Low sides on (LS brake)  |

| 0   | 1   | 1      | 1     | Off | On  | On  | Off | Reverse                  |

| 1   | 0   | 1      | 1     | On  | Off | Off | On  | Forward                  |

| 1   | 1   | 1      | 1     | On  | Off | On  | Off | High sides on (HS brake) |

| X   | X   | 0      | Х     | Off | Off | Off | Off | Coast                    |

| 0   | 0   | 1      | 0     | On  | Off | Off | Off | FETs diagnostic (Q1 on)  |

| 0   | 1   | 1      | 0     | Off | Off | Off | On  | FETs diagnostic (Q4 on)  |

| 1   | 1   | 1      | 0     | Off | On  | Off | Off | FETs diagnostic (Q2 on)  |

| 1   | 0   | 1      | 0     | Off | Off | On  | Off | FETs diagnostic (Q3 on)  |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

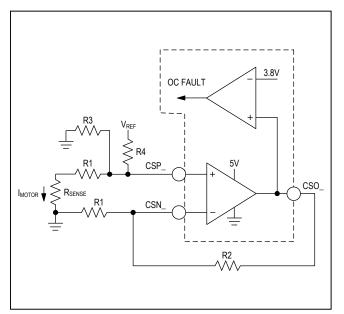

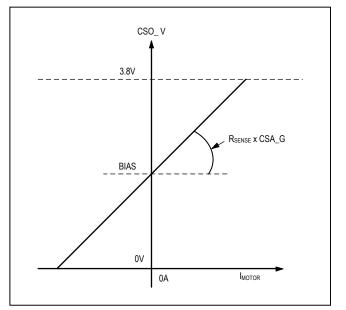

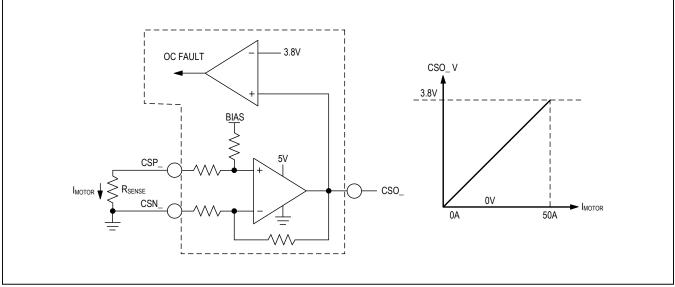

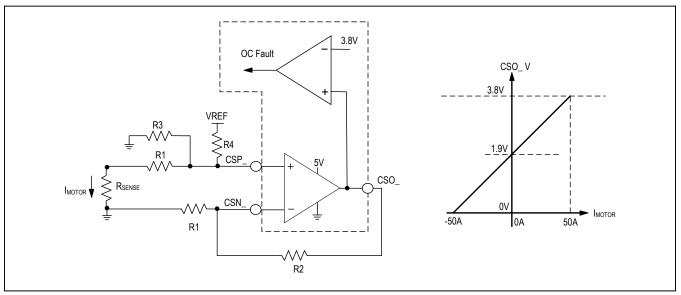

#### Current-Sense Amplifier and Overcurrent Detection

The H-bridge current is sensed by the low-side currentsense amplifier. The open-loop gain of the current-sense amplifier is 110dB and the closed-loop gain of this amplifier is set with external resistors (CSA\_G) according to:

CSA\_G = R2/R1+1 with R3//R4 = R2

With additional external resistors, it is possible to add a bias voltage to the CSO\_ output to enable negative current monitoring during fast decay:

$$BIAS = V_{RFF} \times [R3/(R3 + R4)]$$

The values of R1–R4 must be chosen in accordance with Table 4 in order to pass the power-up diagnostic test.

An overcurrent fault is triggered when the output of the current-sense amplifier (CSO\_) reaches 3.8V. The motor overcurrent value can be estimated with the following formula:

$I_{MOTOR OC} = (3.8V - BIAS)/(R_{SENSE} \times CSA_G)$

The application circuit for a slow-decay case ( $I_{MOTOR}$  always positive) is shown in Figure 7.

The application circuit for a fast-decay case ( $I_{MOTOR}$  is positive and negative) is shown in Figure 8.

CSA\_G = 19, BIAS = 1.9V, CSA Closed-Loop Bandwidth = 1.6MHz

Figure 5. Current-Sense Amplifier (Typical Configuration)

Figure 6. Current-Sense Amplifier Output Characteristics

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

Figure 7. Current-Sense Amplifier Configuration (Positive Current Only)

Figure 8. Current-Sense Amplifier Configuration (Bidirectional Current Flow)

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

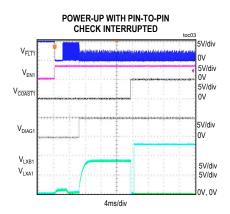

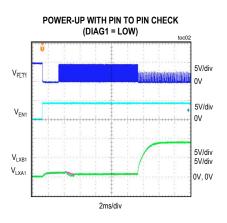

#### Power-Up Diagnostic Mode

After power-up, every time EN\_ goes high with DIAG\_ low, the diagnostic power-up routine starts. The device performs the following checks for each pin:

- · Is the pin shorted to ground?

- · Is the pin open?

- · Is the pin shorted to an adjacent pin?

The diagnostic strategy is based on a sequential routine that starts from the  $V_{DSTH}$  pin and proceeds counterclockwise to end at the COAST\_ pin. In the event of a diagnostic error during the sequential check, the diagnostic sequence is terminated and an ASIL fault is declared at the FLT\_ pin by forcing the duty of the output signal to 25%. Pins LX\_, DH\_, DL\_, BST\_, SUP\_, and LS\_ are not checked during this power-up diagnostic routine. Their functionality can be verified during the FET diagnostic mode, as described in the *FET Diagnostic Mode* section.

#### **FET Diagnostic Mode**

During normal operation (after power-up is completed, EN\_ pin high), FET diagnostic mode can be entered by forcing  $\overline{DIAG}$  = 0. The LXA\_ and LXB\_ pins are then connected through an internal 1k $\Omega$  (typ) pulldown/ pullup to PGND\_/SUP\_, based on the selected FET under diagnosis.

$V_{DS}$  fault and overcurrent event can be used to check the motor and H-bridge status in FET diagnostic mode.

#### Table 4. Power-Up Diagnostic Pin Setting

| PIN                 | CONDITION TO PASS POWER-UP TEST                                                    |

|---------------------|------------------------------------------------------------------------------------|

| CR_                 | 3.3µF ±10% ceramic capacitor connected to ground.                                  |

| CSP_                | Place an equivalent resistance with a value between 500 $\Omega$ and 2k $\Omega$ . |

| CSN_                | Place an equivalent resistance with a value between 500 $\Omega$ and 2k $\Omega$ . |

| CSO_                | Place a feedback resistance with a value between $5k\Omega$ and $100k\Omega$ .     |

| PGND_               | Connect to the ground plane of the system board.                                   |

| SLEW_               | Place a resistance with a value between $10k\Omega$ and $200k\Omega$ .             |

| DT_                 | Place a resistance with a value between $10k\Omega$ and $200k\Omega$ .             |

| V <sub>DSTH</sub> _ | Place an equivalent resistance with a value between $500\Omega$ and $10k\Omega$ .  |

| FLT_                | Connect a resistance with a value between $1k\Omega$ and $3.3k\Omega$ to IN        |

| EN_                 | Connect to IN_ through external driving circuitry.                                 |

| DIAG_               | Connect to AGND_/PGND_ or IN_ through external driving circuitry.                  |

| PA_                 | Connect to AGND_/PGND_ through external driving circuitry.                         |

| PB_                 | Connect to IN_ through external driving circuitry.                                 |

| COAST_              | Connect to AGND_/PGND_ through external driving circuitry.                         |

#### Table 5. FET Control

| COAST_ | PA_ | PB_ | FET ON | LXA_ STATUS          | LXB_ STATUS    |

|--------|-----|-----|--------|----------------------|----------------|

| 1      | 0   | 0   | Q1     | Pulldown to ground   | Hi-Z           |

| 1      | 1   | 1   | Q2     | Pullup to SUP_       | Hi-Z           |

| 1      | 1   | 0   | Q3     | Hi-Z Pulldown to gro |                |

| 1      | 0   | 1   | Q4     | Hi-Z                 | Pullup to SUP_ |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### Table 6. Interpreting Fault Information in Diagnostic Mode

| TURNED ON nMOS | V <sub>DS</sub> FAULT                         | V <sub>DS</sub> AND OVERCURRENT EVENT |

|----------------|-----------------------------------------------|---------------------------------------|

| Q1             | Q1 open or motor terminal A shorted to ground | Q2 shorted                            |

| Q2             | Q2 open or motor terminal A shorted to SUP_   | Q1 shorted                            |

| Q3             | Q3 open or motor terminal B shorted to ground | Q4 shorted                            |

| Q4             | Q4 open or motor terminal B shorted to SUP_   | Q3 shorted                            |

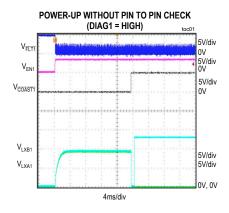

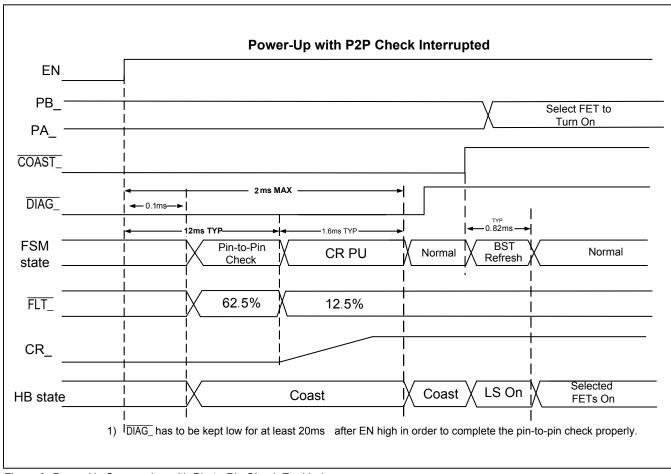

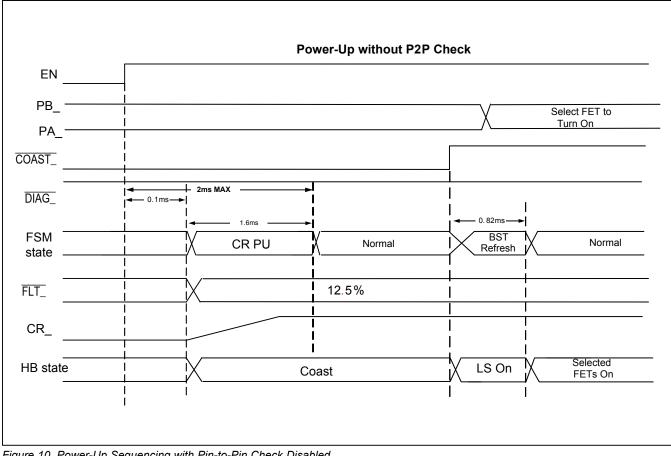

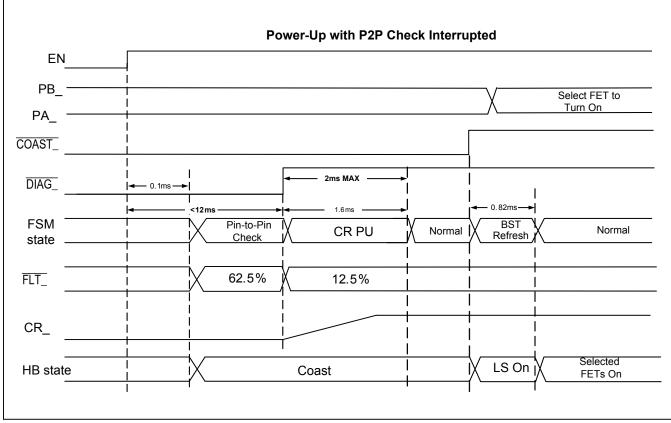

#### **Power-Up Scenarios**

See Figure 9, Figure 10, and Figure 11 for power-up scenarios.

Figure 9. Power-Up Sequencing with Pin-to-Pin Check Enabled

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

Figure 10. Power-Up Sequencing with Pin-to-Pin Check Disabled

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

Figure 11. Power-Up Sequencing with Pin-to-Pin Check Interrupted

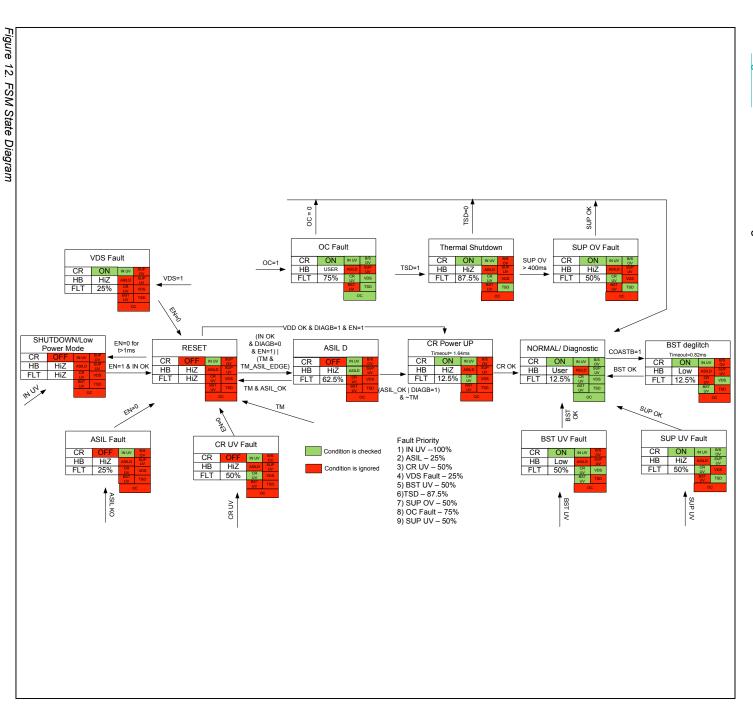

State Diagram See Figure 12 for Figure 12 for the FSM state diagram.

Downloaded from: http://www.datasheetcatalog.com/

www.maximintegrated.com

Maxim Integrated \_\_\_\_ 24

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **BST Fault**

A BST fault is detected (except in coast mode, when it is masked) when the voltage on any of the BST\_ capacitors falls below 7V (typ). When this happens, normal operation of the H-bridge is impossible until the BST\_ capacitor is recharged. To avoid faults due to undervoltage on the boost (BST\_) capacitors, a BST fault deglitch timer is incorporated in the device. At each low-to-high transition of the COAST\_ pin, the deglitch timer is activated. During the deglitch time, the internal logic of the device takes control and the DLA and DLB outputs are forced high in order to turn on the external low-side MOSFETs and refresh the charge on the boost capacitors. When this timer elapses, the bootstrap capacitors are fully charged and ready to operate the motor.

When a BST fault occurs (in the absence of faults), it is normally sufficient to perform a boost-capacitor refresh by taking COAST\_ low and then high again and waiting at least 0.9ms until the BST fault deglitch timer elapses.

#### V<sub>DS</sub> Fault

Every time an FET of the H-bridge is turned on, a dedicated drain-source comparator checks if its drain-source voltage is lower or higher than the V<sub>DS</sub> voltage threshold set through the V<sub>DSTH</sub> pin. If the FET drain-source voltage is higher than the voltage on the V<sub>DSTH</sub> pin, a fault is detected. To avoid false error detection, the V<sub>DS</sub> comparators are inhibited after MOSFET power-on for a blanking time (t<sub>BLANK</sub>). Connect V<sub>DSTH</sub> to IN\_ to disable the V<sub>DS</sub> fault-detection circuitry.

#### SUP\_ Undervoltage and Overvoltage Protections

The device includes undervoltage and overvoltage detection circuitry on the SUP\_ pins. If the voltage is less than 4.5V, a SUP\_ undervoltage fault is signaled through the FLT\_ pin and all the MOSFET drivers are turned off. If the SUP\_ voltage exceeds 35V for more than 400ms, a SUP\_ overvoltage fault is detected and all the drivers are turned off (H-bridge).

#### **Fault Behavior**

The FLT\_ pin indicates detected faults by means of a 625kHz signal, with varying duty cycle according to Table 7.

#### Table 7. Fault Classes and the FLT\_ Output

| FAULT CLASS | FAULT DESCRIPTION                                  | DUTY CYCLE OF FLT_ (%) |

|-------------|----------------------------------------------------|------------------------|

| 1           | None                                               | 12.5                   |

| 2           | V <sub>DS</sub> fault, ASIL fault                  | 25                     |

| 3           | SUP_ overvoltage (SUP_, CR_ and BST_ undervoltage) | 50                     |

| 1           | None (pin-to-pin check routine ongoing)            | 62.5                   |

| 4           | Overcurrent                                        | 75                     |

| 5           | Thermal shutdown                                   | 87.5                   |

| 6           | IN_ undervoltage                                   | 100                    |

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### Table 8. Fault Summary

| FAULT                                   | FAULT DESCRIPTION                                    | DUTY<br>CYCLE (%) | CR_ | H-BRIDGE<br>FETs STATE | LATCHED | FAULT<br>RESET   |

|-----------------------------------------|------------------------------------------------------|-------------------|-----|------------------------|---------|------------------|

| None                                    | _                                                    | 12.5              | On  | User control           | No      | _                |

| Overcurrent                             | V <sub>CSO</sub> _ > 3.8V                            | 75                | On  | User control           | No      | _                |

| $V_{DS}$ fault ( $\overline{DIAG}$ = X) | FET on-drain source<br>voltage > V <sub>DSTH</sub> _ | 25                | On  | Off (coast*)           | Yes     | EN_ low<br>pulse |

| IN_ undervoltage                        | V <sub>IN</sub> _ < V <sub>INUV</sub>                | 100               | Off | Off (coast*)           | No      | _                |

| CR_ undervoltage                        | CR_ < V <sub>CRUV</sub>                              | 50                | Off | Off (coast*)           | Yes     | EN_ low<br>pulse |

| BSTA_/BSTB_<br>undervoltage             | BSTLX_ <v<sub>BSTUV</v<sub>                          | 50                | On  | DLA_, DLB_<br>high     | No      | _                |

| SUP_ undervoltage                       | SUP_ < V <sub>SUPUV</sub>                            | 50                | On  | Off (coast*)           | No      | _                |

| SUP_ overvoltage                        | SUP_ > 36V for t > 400ms                             | 50                | On  | Off (coast*)           | No      | _                |

| Thermal shutdown                        | T <sub>J</sub> > T <sub>JTSD</sub>                   | 87.5              | On  | Off (coast*)           | No      | —                |

\*Coast = Motor in Hi-Z.

#### **Applications Information**

#### **Power Dissipation**

To evaluate the device's power consumption, it is necessary to calculate the total supply current from the supply input pin (IN\_) for a single channel:

$$I_{IN} = I_{IN Q} + 4 \times Q_G \times f_{PWM}$$

where  $I_{IN_Q}$  is the quiescent current,  $Q_G$  is the total gate charge of the external nMOS, and  $f_{PWM}$  is the PWM switching frequency.

The device's total power dissipation is then (for both channels):

$$PD = 2 \times [V_{IN} \times I_{IN}]$$

#### **Layout Guidelines**

For best performance, it is advisable to use the following guidelines when designing the PCB for the MAX20082:

• Use separate analog ground (AGND) and power ground (PGND) planes and connect them at a single point. Implement connections between the same grounds on different layers with multiple vias.

- Maintain the input and output power sections (connections to SUP\_, LXA\_, LXB\_, and LS\_) as compact as possible.

- Use wide traces to connect the components related to the high-current paths.

- Use multiples vias to connect high-current paths that must pass from one layer to another.

- Make the MOSFET gate-drive traces (DHA\_, DHB\_, DLA\_, and DLB\_) as short as possible and use large track widths.

- Place the boost capacitors (between CP\_ and CN\_), charge-pump output capacitors (on CR\_), and the input capacitors (on IN\_) close to the IC and connect them without using vias.

- The current-sense connections should be Kelvin connected.

Contact your Maxim Integrated representative for further details on choosing and placing external components.

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

# **Typical Application Circuit (1 Channel Shown)**

# Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

### **Ordering Information**

| PART            | TEMP RANGE      | PIN-PACKAGE |

|-----------------|-----------------|-------------|

| MAX20082AUN/V+T | -40°C to +125°C | 56 TSSOP    |

*N* denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

#### **Chip Information**

PROCESS: BICMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE  | PACKAGE | OUTLINE        | LAND PATTERN   |

|----------|---------|----------------|----------------|

| TYPE     | CODE    | NO.            | NO.            |

| 56 TSSOP | U56N+2C | <u>21-0481</u> | <u>90-0338</u> |

### Dual, Redundant, H-Bridge Motor Driver with ASIL Diagnostics

#### **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 8/14     | Initial release | —       |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2014 Maxim Integrated Products, Inc. | 29